## MC9S08AC16

参考手册

苏州大学飞思卡尔嵌入式系统研发中心翻译

http://sumcu.suda.edu.cn

2009年11月

## MC9S08AC16 系列特点

#### MC9S08AC16 系列特点

- 消费&工业

- MC9S08AC16

- MC9S08AC8

- 汽车

- MC9S08AW16A

- MC9S08AW8A

#### 8 位 HCS08 中央处理单元 (CPU)

- 40-MHz HCS08CPU(中央处理单元)

- 20-MHz 内部总线频率

- HC08 指令集,增加了 BGND 指令

- 背景调试系统

- 在线调试(in-circuit debugging)期间可以设置单个断点(在片上调试模式时可以在增加两个 断点)

- 调试模式包括 2 个比较仪和 9 个触发器模式。8 个 FIFO 来存储流控制地址和事件数据。调试模式支持标签和强制断点

- 支持高达 32 个中断/复位源

#### 存储器选项

- 高达 16KB 的片上在线可编程 FLASH 存储器,有块保护和安全选项

- 高达 1KB 的片上 RAM

#### 时钟源选项

● 时钟源选项包括晶体、蜂鸣器、外部时钟、或能够 NVM 调整的精确的内部集成时钟

#### 系统保护

- 可选的系统正常操作(COP)复位,使用独立的内部时钟源或总线时钟运行

- 低压检测复位或中断

- 非法操作符检测复位

- 非法地址检测复位

#### 省电模式

● 增加了两种停止模式

#### 外部设备

- ADC-8 通道, 10 位 AD 转换器,包含自动比较功能

- SCI-两个串行通信接口模块,可选的 13 位停止符

- SPI-串行外设接口模块

- IIC-内部集成电路总线模块,可以工作在 100kps 的最大总线负载上,减少负载将会允许更高

的波特率

- 定时器-3 个 16 位定时器/脉宽调制 (TPM) 模块-2 个 2 通道和 1 个 4 通道;每个定时器在每个通道上都有可选的输入捕捉,输出比较,PWM。每个定时器在每个通道上都可以配置为带缓冲,中心 PWM (CPWM)

- KBI-7 引脚键盘中断模块

#### 输入/输出

- 高达 38 个通用输入/输出(I/O)引脚

- 输入时,每个端口都有软件选择的上拉电阻

- 输出时,每个端口都有软件选择的转换速率控制

- 输出时,每个端口都有软件选择的驱动强度

- 主机复位引脚和上电复位 (POR)

- RESET, IRQ, BKGD/MS 引脚在内部上拉以减小系统消耗

#### 封装选择

- 48 引脚 QFN

- 44 引脚 LQFP

- 32 引脚 LQFP

# 目 录

| 第一章 绪论                                                                               |    |

|--------------------------------------------------------------------------------------|----|

| 1.1 概述                                                                               | 12 |

| 1.2 MCU 结构框图                                                                         | 12 |

| 1.3 系统时钟分配                                                                           | 14 |

| 第二章 引脚及其连接                                                                           | 15 |

| 2.1 简介                                                                               | 15 |

| 2.2 设备的管脚分配                                                                          |    |

| 2.3 推荐的系统连接                                                                          |    |

| 2.3.1 电源(V <sub>DD</sub> 、2×V <sub>SS</sub> 、V <sub>DDAD</sub> 和 V <sub>SSAD</sub> ) |    |

| 2.3.2 振荡器(XTAL 与 EXTAL)                                                              |    |

| 2.3.3 复位                                                                             |    |

| 2.3.4 背景/模式选择(BKGD/MS)                                                               |    |

| 2.3.5 ADC 参考引脚(V <sub>REFH</sub> 与 V <sub>REFL</sub> )                               |    |

| 2.3.6 外部的中断引脚(IRQ)                                                                   |    |

| 2.3.7 通用 I/O 及外设端口                                                                   | 20 |

| 第三章 工作模式                                                                             | 21 |

| 3.1 简介                                                                               | 21 |

| 3.2 特征                                                                               |    |

| 3.3 运行模式                                                                             |    |

| 3.4 背景调试模式                                                                           |    |

| 3.5 等待模式                                                                             |    |

| 3.6 停止模式                                                                             |    |

| 3.6.1 Stop2 模式                                                                       |    |

| 3.6.2 Stop3 模式                                                                       |    |

| 3.6.3 停止模式下激活 BDM 使能                                                                 |    |

| 3.6.4 停止模式下 LVD 使能                                                                   |    |

| 3.6.5 停止模式下的片上外设模块                                                                   | 24 |

| 第四章 片上存储器                                                                            | 26 |

| 4.1 简介 MC9SAC16 系列存储映像                                                               | 26 |

| 4.1.1 复位和中断向量分配                                                                      | 26 |

| 4.2 寄存器地址和位分配                                                                        | 27 |

| 4.3 RAM                                                                              | 32 |

| 4.4 FLASH                                                                            | 32 |

| 4.4.1 特征                                                                             | 32 |

| 4.4.2 写入和擦除时间                                                                        |    |

| 4.4.3 写入和擦除命令的执     | 行               | 33  |

|---------------------|-----------------|-----|

| 4.4.4 突发模式写入的执行     |                 | 35  |

| 4.4.5 访问错误          |                 | 36  |

| 4.4.6 FLASH 块保护     |                 | 36  |

| 4.4.7 向量重定向         |                 | 37  |

| 4.5 安全性             |                 | 37  |

| 4.6 FLASH 寄存器和控制位   |                 | 38  |

| 4.6.1 FLASH 时钟分频寄存  | 器(FCDIV)        | 38  |

| 4.6.2 FLASH 选项寄存器(F | OPT 和 NVOPT)    | 39  |

| 4.6.3 FLASH 配置寄存器(F | CNFG)           | 40  |

| 4.6.4 FLASH 保护寄存器(F | PROT 和 NVPROT)  | 40  |

| 4.6.5 FLASH 状态寄存器(F | STAT)           | 40  |

| 4.6.6 FLASH 命令寄存器(F | CMD)            | 41  |

| 第五音 复位 山斯和系统配署      |                 | /13 |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     | OP)看门狗          |     |

|                     |                 |     |

|                     |                 |     |

|                     | 脚               |     |

|                     |                 |     |

|                     |                 |     |

|                     | 局部屏蔽            |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     |                 |     |

|                     | 存器和控制位          |     |

|                     | 寄存器(IRQSC)      |     |

|                     | (SRS)           |     |

|                     | 位寄存器(SBDFR)     |     |

|                     | T)              |     |

|                     | F器(SMCLK)       |     |

|                     | (SDIDH、SDIDL)   |     |

|                     | 控制寄存器(SRTISC)   |     |

|                     | 制寄存器 1(SPMSC1)  |     |

|                     | 控制寄存器 2(SPMSC2) |     |

| 5.9.10 系统系统选项寄存器    | 导 2(STOP2)      | 55  |

| 第六章 并行输入和输出         |                 | 56  |

| 6.1 | 简介                                   | 56 |

|-----|--------------------------------------|----|

| 6.2 | 特征                                   | 57 |

| 6.3 | 引脚描述                                 | 58 |

|     | 6.3.1 A □                            | 58 |

|     | 6.3.2 B □                            | 58 |

|     | 6.3.3 C □                            | 58 |

|     | 6.3.4 D □                            |    |

|     | 6.3.5 E □                            |    |

|     | 6.3.6 F □                            |    |

|     | 6.3.7 G 🗆                            |    |

|     | 并行 I/O 控制                            |    |

| 6.5 | 引脚控制                                 |    |

|     | 6.5.1 内部上拉电阻使能                       |    |

|     | 6.5.2 输出转换速率控制使能                     |    |

| ( ( | 6.5.3 输出驱动强度选择<br>停止模式下的引脚           |    |

|     | <ul><li></li></ul>                   |    |

| 0.7 | 开1] I/O 与51 脚径制 司 仔 奋                |    |

|     | 6.7.2 A 口引脚控制寄存器(PTAPE、PTASE、PTADS)  |    |

|     | 6.7.3 B 口 I/O 寄存器(PTBD 和 PTBDD)      |    |

|     | 6.7.4 B 口引脚控制寄存器(PTBPE、PTBSE、PTBDS)  |    |

|     | 6.7.5 C 口 I/O 寄存器(PTCD 和 PTCDD)      |    |

|     | 6.7.6 C 口引脚控制寄存器(PTCPE、PTCSE、PTCDS)  |    |

|     | 6.7.7 D 口 I/O 寄存器(PTDD 和 PTDDD)      |    |

|     | 6.7.8 D 口引脚控制寄存器(PTDPE、PTDSE、PTDDS)  | 68 |

|     | 6.7.9 E 口 I/O 寄存器(PTED 和 PTEDD)      | 69 |

|     | 6.7.10 E 口引脚控制寄存器(PTEPE、PTESE、PTEDS) | 69 |

|     | 6.7.11 F 口 I/O 寄存器(PTFD 和 PTFDD)     | 70 |

|     | 6.7.12 F 口引脚控制寄存器(PTFPE、PTFSE、PTFDS) | 71 |

|     | 6.7.13 G 口 I/O 寄存器(PTGD 和 PTGDD)     |    |

|     | 6.7.14 G 口引脚控制寄存器(PTGPE、PTGSE、PTGDS) | 72 |

| 第七章 | 中央处理单元(S08CPUV2)                     | 74 |

| 7.1 | 介绍                                   | 74 |

|     | 7.1.1 特征                             | 74 |

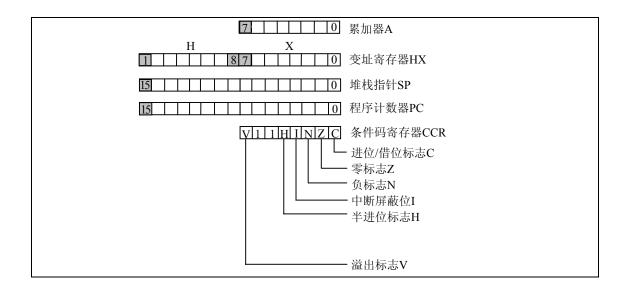

| 7.2 | 编程结构和 CPU 寄存器                        | 74 |

|     | 7.2.1 累加器(A)                         |    |

|     | 7.2.2 索引寄存器(H:X)                     |    |

|     | 7.2.3 堆栈指针 (SP)                      |    |

|     | 7.2.4 程序计数器 (PC)                     |    |

|     | 7.2.5 条件码寄存器(CCR)                    |    |

| 7.3 | 寻址模式                                 |    |

|     | 7.3.1 内在寻址方式(INH)                    |    |

|     | 7.3.2 相对寻址方式(REL)                    |    |

|     | 7.3.3 立即寻址方式(IMM)                    | 77 |

|     | 7.3.4 直接寻址方式(DIR)                                                               | 77  |

|-----|---------------------------------------------------------------------------------|-----|

|     | 7.3.5 扩展寻址方式(EXT)                                                               | 77  |

|     | 7.3.6 变址寻址方式                                                                    | 77  |

|     | 7.3.6.1 无偏移量变址方式(IX)                                                            | 77  |

|     | 7.3.6.2 无偏移量变址、变址加 1 寻址方式(IX+)                                                  | 78  |

|     | 7.3.6.3 8 位偏移量变址方式(IX1)                                                         | 78  |

|     | 7.3.6.48位偏移量变址、变址加1寻址方式(IX1+)                                                   |     |

|     | 7.3.6.5 16 位偏移量变址方式(IX2)                                                        | 78  |

|     | 7.3.6.6 8 位偏移量堆栈寻址方式(SP1)                                                       | 78  |

|     | 7.3.6.7 16 位偏移量堆栈寻址方式(SP2)                                                      | 78  |

| 7.4 | 特殊操作                                                                            | 78  |

|     | 7.4.1 复位序列                                                                      | 78  |

|     | 7.4.2 中断序列                                                                      | 78  |

|     | 7.4.3 等待模式                                                                      | 79  |

|     | 7.4.4 停止模式                                                                      | 79  |

|     | 7.4.5 背景模式                                                                      | 79  |

| 7.5 | HCS08 指令设置摘要                                                                    | 79  |

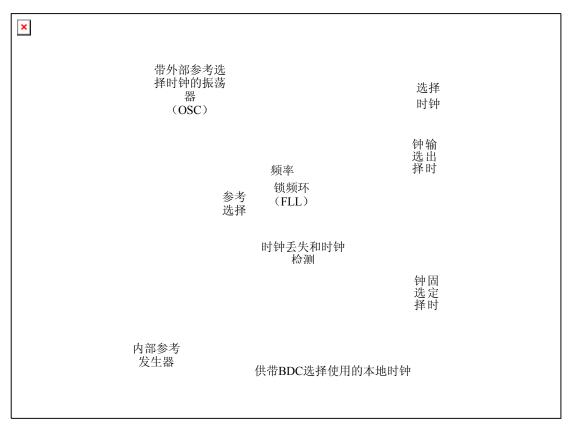

| 第八章 | 内部时钟发生器(S08ICGV4)                                                               | 91  |

|     |                                                                                 |     |

| 8.1 | 介绍                                                                              |     |

|     | 8.1.1 特征                                                                        |     |

|     | 8.1.2 操作方式                                                                      |     |

| 0.2 | 8.1.3 框图<br>外部信号描述                                                              |     |

| 8.2 | 外部信号抽处                                                                          |     |

|     | 8.2.2XTAL—拆荡器输出                                                                 |     |

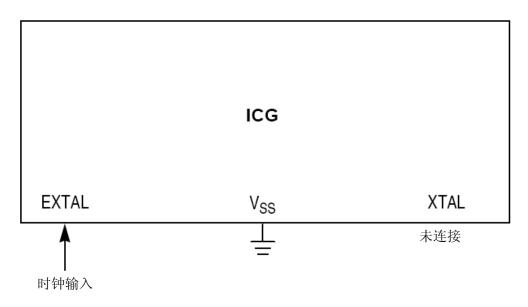

|     | 8.2.3 外部时钟连接                                                                    |     |

|     | 8.2.4 外部晶振/共鸣器连接                                                                |     |

| 0.2 | 寄存器定义                                                                           |     |

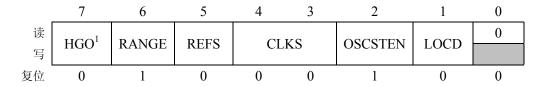

| 8.3 | 9.3.1 ICG 控制寄存器 1(ICGC1)                                                        |     |

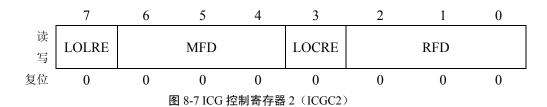

|     | 8.3.2 ICG 控制寄存器 2(ICGC2)                                                        |     |

|     | 8.3.3 ICG 状态寄存器 1(ICGS1)                                                        |     |

|     | 8.3.4 ICG 状态寄存器 2(ICGS2)                                                        |     |

|     | 8.3.5 ICG 滤波器寄存器(ICGFLTU、ICGFLTL)                                               |     |

|     | 8.3.6 ICG 调整寄存器(ICGTRM)                                                         |     |

| Q 1 | 功能性描述                                                                           |     |

| 0.4 | 8.4.1 关模式                                                                       |     |

|     | 8.4.1.1 活跃 BDM                                                                  |     |

|     | 8.4.1.2 OSCSTEN 位设置                                                             |     |

|     | 8.4.1.3 停止/关模式恢复                                                                |     |

|     | 8.4.2 自时钟模式(SCM)                                                                |     |

|     | 8.4.3 FLL 内部时钟模式(FEL)                                                           |     |

|     | 8.4.4 FLL 内部失锁                                                                  |     |

|     | 8.4.5 FLL 内部锁定                                                                  |     |

|     | 8.4.6 FLL 旁路外部时钟模式(FBE)                                                         |     |

|     | - V・・・V × シャ フォアロフ   HPパオヤ   I人どV   \ 1 リコノ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 102 |

|     | 8.4.7 FLL 外部时钟模式(FEE)                 | 102 |

|-----|---------------------------------------|-----|

|     | 8.4.7.1 FLL 外部失锁                      | 103 |

|     | 8.4.7.2 FLL 外部锁定                      | 103 |

|     | 8.4.8 FLL 锁和锁丢失检测                     | 103 |

|     | 8.4.9 FLL 时钟丢失检测                      | 103 |

|     | 8.4.10 时钟模式必要条件                       | 104 |

|     | 8.4.11 固定频率时钟                         |     |

|     | 8.4.12 高增益振荡器                         | 105 |

| 8.5 | 5 初始化/应用信息                            | 105 |

|     | 8.5.1 简介                              |     |

|     | 8.5.2 例 1:外部晶振=32kHz,总线频率=4.19MHz     | 106 |

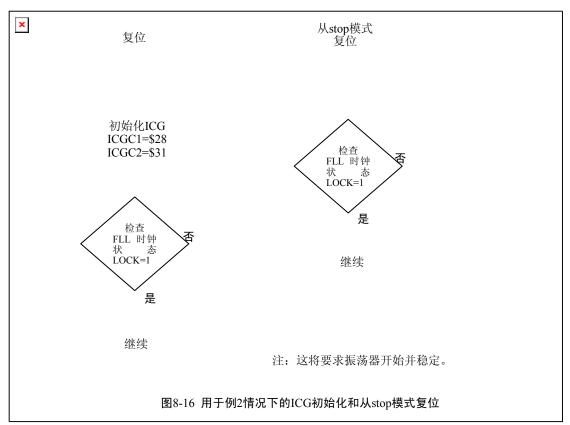

|     | 8.5.3 例 2: 外部晶振=4MHz,总线频率=20MHz       | 108 |

|     | 8.5.4 例 3: 无外部晶振,总线频率=5.4MHz          |     |

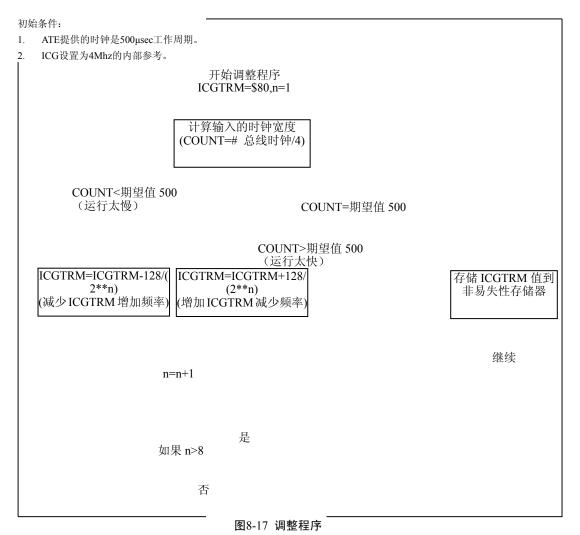

|     | 8.5.5 例 4: 内部时钟产生器调整                  | 110 |

| 第九章 | 键盘中断(S08KBIV1)                        | 112 |

| 9.1 | 「                                     | 112 |

| 9.2 | 2 键盘引脚复用                              | 112 |

| 9.3 | 3 特征                                  | 112 |

|     | 9.3.1 KBI 框图                          | 113 |

| 9.4 | 4 寄存器定义                               | 114 |

|     | 9.4.1 KBI 状态控制寄存器(KBISC)              | 114 |

|     | 9.4.2 KBI 引脚使能寄存器(KBIPE)              | 115 |

| 9.5 | 5 功能描述                                | 115 |

|     | 9.5.1 引脚使能                            | 115 |

|     | 9.5.2 边沿和电平触发                         |     |

|     | 9.5.3 KBI 中断控制                        | 115 |

| 第十章 | 定时器/脉宽调制(S08TPMV3)                    | 116 |

| 10. | .1 简介                                 | 116 |

| 10. | 2 特征                                  | 116 |

| 10. | .3 TPMV3 与以前版本的区别                     | 117 |

|     | 10.3.1 TPMV1 的变换                      | 119 |

|     | 10.3.2 特征                             | 119 |

|     | 10.3.3 操作模式                           | 120 |

|     | 10.3.4 框图                             | 120 |

| 10. | .4 信号描述                               |     |

|     | 10.4.1 详细信号描述                         |     |

|     | 10.4.1.1 EXTCLK——外部时钟源                |     |

|     | 10.4.1.2 TPMxCHn——TPM 通道 n 输入输出引脚     |     |

| 10. | .5 寄存器定义                              |     |

|     | 10.5.1 TPM 状态和控制寄存器 (TPMxSC)          |     |

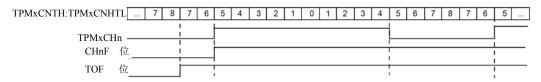

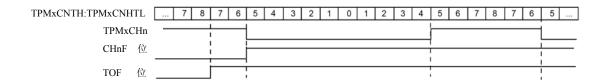

|     | 10.5.2 TPM 计数器寄存器(TPMxCNTH:TPMxCNHTL) |     |

|     | 10.5.3 TPM 计数器模寄存器(TPMxMODH:TPMxMODL) |     |

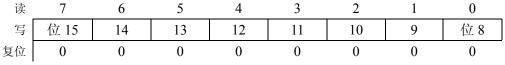

|     | 10.5.4 TPM 通道 n 状态和控制寄存器(TPMxCnSC)    | 127 |

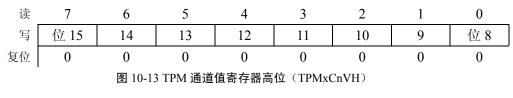

|    | 10.5.5 TPM 通道值寄存器(TPMxCnVH : TPMxCnVL) | 128 |

|----|----------------------------------------|-----|

|    | 10.6 功能描述                              | 129 |

|    | 10.6.1 计数器                             | 129 |

|    | 10.6.1.1 计数器时钟源                        | 129 |

|    | 10.6.1.2 计数器溢出和模块复位                    | 129 |

|    | 10.6.1.3 计数模式                          | 130 |

|    | 10.6.1.4 手动计数器复位                       | 130 |

|    | 10.6.2 通道模式选择                          | 130 |

|    | 10.6.2.1 输入捕捉模式                        | 130 |

|    | 10.6.2.2 输出比较模式                        | 130 |

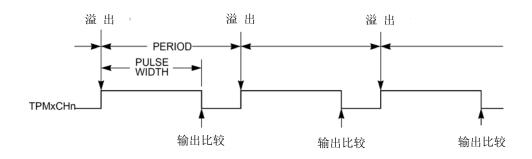

|    | 10.6.2.3 边对齐 PWM 模式                    | 131 |

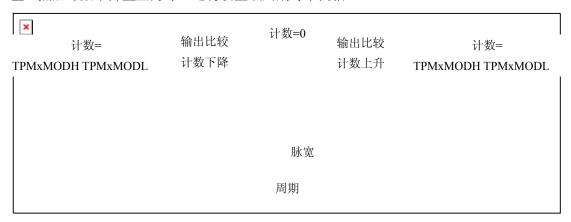

|    | 10.6.2.4 中心对齐 PWM 模式                   | 131 |

|    | 10.7 复位概述                              | 133 |

|    | 10.7.1 概要                              | 133 |

|    | 10.7.2 复位操作描述                          | 133 |

|    | 10.8 中断                                | 133 |

|    | 10.8.1 概述                              | 133 |

|    | 10.8.2 中断操作描述                          | 133 |

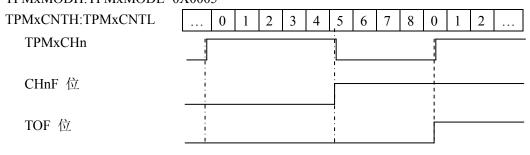

|    | 10.8.2.1 定时器溢出中断(TOF)描述                | 133 |

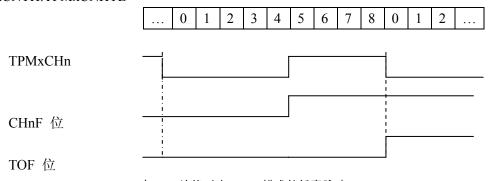

|    | 10.8.2.1.1 通常情形                        | 133 |

|    | 10.8.2.1.2 中心对齐 PWM 情形                 | 134 |

|    | 10.8.2.2 通道事件中断描述                      | 134 |

|    | 10.8.2.2.1 输入捕捉事件                      | 134 |

|    | 10.8.2.2.2 输出比较事件                      | 134 |

|    | 10.8.2.2.3 PWM 结束占空比事件                 | 134 |

| 第十 | 一章 串行通信接口(S08SCIV4)                    | 135 |

|    | 11.1 简介                                | 135 |

|    | 11.1.1 特征                              | 136 |

|    | 11.1.2 操作模式                            |     |

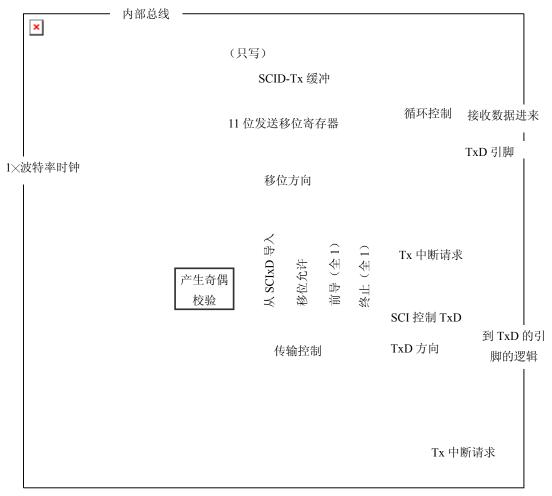

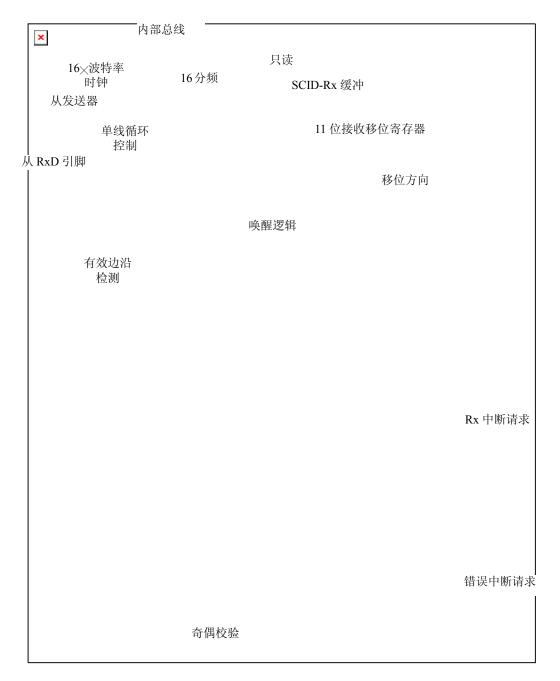

|    | 11.1.3 框图                              | 137 |

|    | 11.2 寄存器定义                             | 139 |

|    | 11.2.1 SCI 波特率寄存器(SCIxBDH、SCIxBDL)     | 139 |

|    | 11.2.2 SCI 控制寄存器 1(SCIxC1)             | 140 |

|    | 11.2.3 SCI 控制寄存器 2(SCIxC2)             | 141 |

|    | 11.2.4 SCI 状态寄存器 1(SCIxS1)             | 142 |

|    | 11.2.5 SCI 状态寄存器 2(SCIxS2)             | 143 |

|    | 11.2.6 SCI 控制寄存器 3(SCIxC3)             | 144 |

|    | 11.2.7 SCI 数据寄存器(SCIxD)                | 145 |

|    | 11.3 功能描述                              |     |

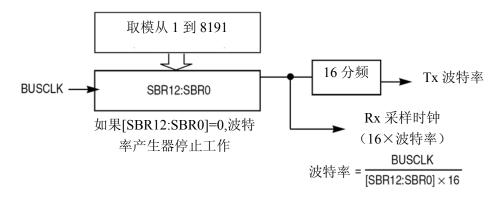

|    | 11.3.1 波特率产生                           | 145 |

|    | 11.3.2 发送功能描述                          |     |

|    | 11.3.2.1 发送终止和等待空闲                     |     |

|    | 11.3.3 接收功能描述                          |     |

|    | 11.3.3.1 数据采样技术                        |     |

|    |                                        |     |

|      | 11.3.3.2 接收唤醒操作            | 147 |

|------|----------------------------|-----|

|      | 11.3.4 中断和状态标志             | 148 |

|      | 11.3.5 其他 SCI 功能           | 148 |

|      | 11.3.5.18位和9位数据模式          | 148 |

|      | 11.3.5.2 停止模式操作            | 149 |

|      | 11.3.5.3 循环模式              | 149 |

|      | 11.3.5.4 单线操作              | 149 |

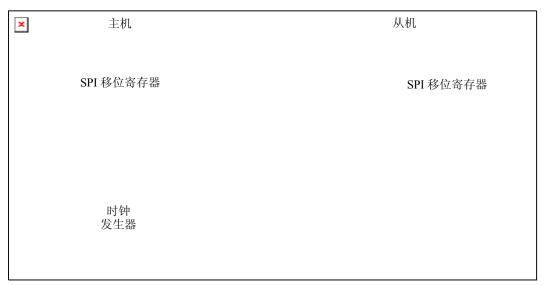

| 第十二章 | 章 串行外设接口(S08SPIV3)         | 150 |

| 12   | 1 简介                       | 150 |

| 1.2. | 12.1.1 特征                  |     |

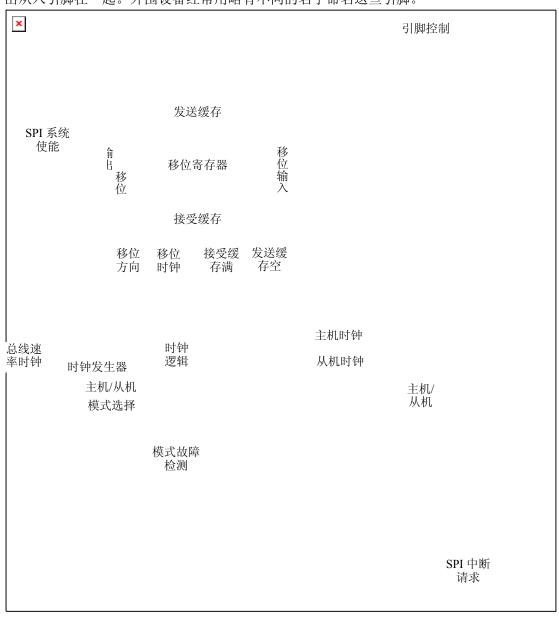

|      | 12.1.2 框图                  |     |

|      | 12.1.2.1 SPI 系统框图          |     |

|      | 12.1.2.2 SPI 模块框图          |     |

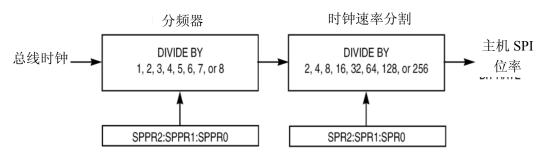

|      | 12.1.3 SPI 波特率发生器          | 154 |

| 12.2 | 2 外部信号描述                   |     |

|      | 12.2.1 SPSCK — SPI 串行时钟    | 154 |

|      | 12.2.2 MOSI — 主入从出引脚       | 154 |

|      | 12.2.3 MISO — 主入从出引脚       |     |

|      |                            | 155 |

| 12.3 | 3 操作模式                     | 155 |

|      | 12.3.1 停止模式中的 SPI          | 155 |

| 12.4 | 4 寄存器定义                    | 155 |

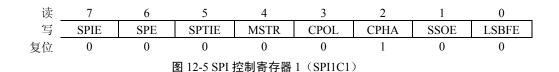

|      | 12.4.1 SPI 控制寄存器 1(SPI1C1) | 155 |

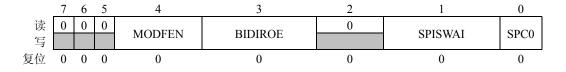

|      | 12.4.2 SPI 控制寄存器 2(SPI1C2) | 156 |

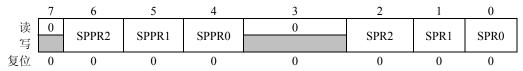

|      | 12.4.3 SPI 比特率寄存器(SPI1BR)  | 157 |

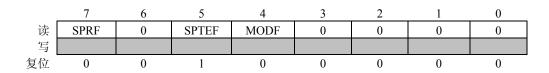

|      | 12.4.4 SPI 状态寄存器(SPI1S)    | 158 |

|      | 12.4.5 SPI 数据寄存器(SPI1D)    | 159 |

| 12.5 | 5 功能性描述                    |     |

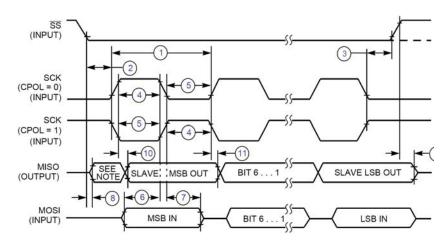

|      | 12.5.1 SPI 时钟格式            | 159 |

|      | 12.5.2 SPI 中断              | 161 |

|      | 12.5.3 模式故障检测              |     |

| 第十三章 | 章 IIC 总线(S08IICV2)         |     |

| 13.  | 1 简介                       |     |

|      | 13.1.1 特征                  |     |

|      | 13.1.2 操作模式                |     |

|      | 13.1.3 框图                  |     |

| 13.2 | 2 外部信号描述                   |     |

|      | 13.3.1 SCL—串行时钟线           |     |

|      | 13.2.2 SDA—串行数据线           |     |

| 13.3 | 3 寄存器定义                    |     |

|      | 13.3.1 IIC 地址寄存器(IIC1A)    |     |

|      | 13.3.2 IIC 频率分频寄存器(IIC1F)  |     |

|               |      | 13.3.3 IIC 控制寄存器(IIC1C1)         | . 168 |

|---------------|------|----------------------------------|-------|

|               |      | 13.3.4 IIC 状态寄存器(IIC1S)          | . 169 |

|               |      | 13.3.5 IIC 数据输入输出寄存器(IIC1D)      | . 170 |

|               |      | 13.3.6 IIC 控制寄存器 2(IIC1C2)       | . 170 |

|               | 13.4 | 功能性描述                            | . 171 |

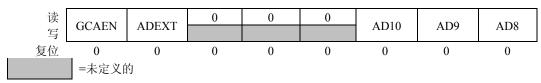

|               |      | 13.4.1 IIC 协议                    | . 171 |

|               |      | 13.4.1.1 开始信号                    | . 172 |

|               |      | 13.4.1.2 从机地址传送                  | . 172 |

|               |      | 13.4.1.3 数据发送                    | . 172 |

|               |      | 13.4.1.4 停止信号                    | . 173 |

|               |      | 13.4.1.5 重新开始信号                  | . 173 |

|               |      | 13.4.1.6 仲裁程序                    | . 173 |

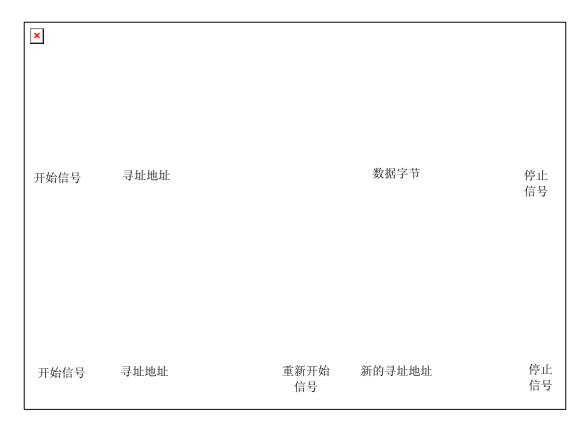

|               |      | 13.4.1.7 时钟同步                    | . 173 |

|               |      | 13.4.1.8 握手                      | . 174 |

|               |      | 13.4.1.9 时钟扩展                    | . 174 |

|               |      | 13.4.2 10-位地址                    | . 174 |

|               |      | 13.4.2.1 主机发送从机接收                | . 174 |

|               |      | 13.4.2.2 主机接收从机发送                | . 175 |

|               |      | 13.4.3 一般寻址                      | . 175 |

|               | 13.5 | 复位                               | . 175 |

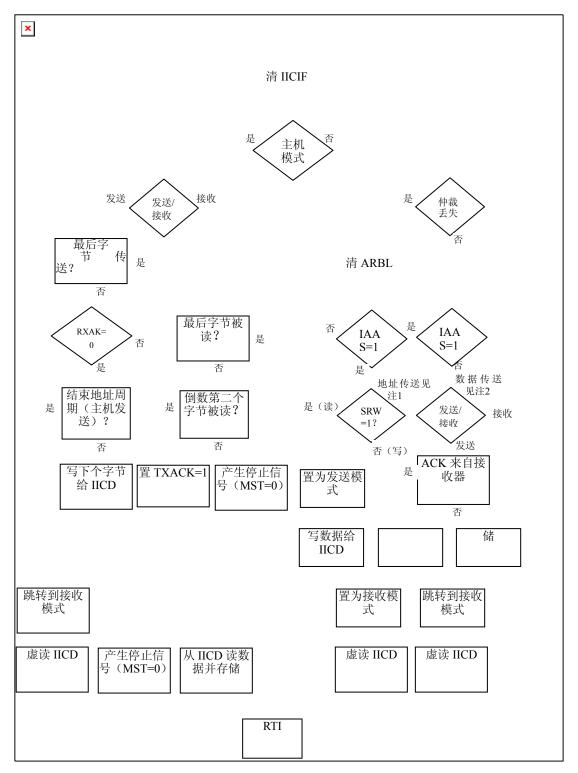

|               | 13.6 | 中断                               | . 175 |

|               |      | 13.6.1 字节传送中断                    | . 176 |

|               |      | 13.6.2 地址检测中断                    | . 176 |

|               |      | 13.6.3 仲裁丢失中断                    | . 176 |

|               | 13.7 | 初始化/应用信息                         | . 176 |

| 笹⊣            | 上川音  | î AD 转换器(S08ADC10V1)             | 170   |

| <b>य</b> ग् । |      |                                  |       |

|               |      | 概述                               |       |

|               | 14.2 | 通道分配                             |       |

|               |      | 14.2.1 交替时钟                      |       |

|               |      | 14.2.2 硬件触发器                     |       |

|               |      | 14.2.2.1 模拟引脚使能                  |       |

|               |      | 14.2.2.2 低功耗模式操作                 |       |

|               |      | 14.2.3 温度传感器                     |       |

|               |      | 14.2.4 特点                        |       |

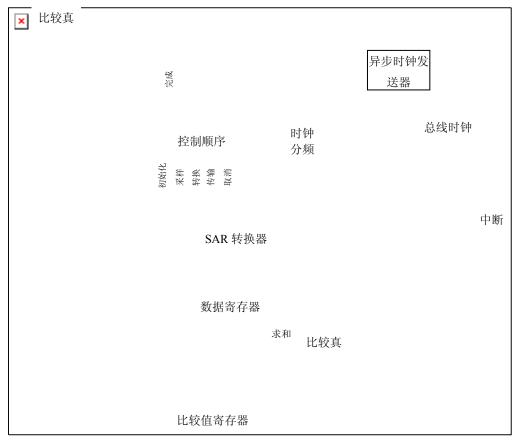

|               |      | 14.2.5 框图                        |       |

|               | 14.3 | 外部信号描述                           |       |

|               |      | 14.3.1 模拟电源(V <sub>DDAD</sub> )  |       |

|               |      | 14.3.2 模拟地(V <sub>SSAD</sub> )   |       |

|               |      | 14.3.3 参考高电压(V <sub>REFH</sub> ) |       |

|               |      | 14.3.4 参考低电压(V <sub>REFL</sub> ) |       |

|               |      | 14.3.5 模拟通道输入(ADx)               |       |

|               | 14.4 | 寄存器定义                            |       |

|               |      | 14.4.1 状态和控制寄存器 1(ADC1SC1)       |       |

|               |      | 14.4.2 状态和控制寄存器 2(ADC1SC2)       | . 185 |

| 14.4.3 数据高结果寄存器(ADC1RH)       |     |

|-------------------------------|-----|

| 14.4.4 数据低结果寄存器(ADC1RL)       | 186 |

| 14.4.5 比较值高寄存器(ADC1CVH)       |     |

| 14.4.6 比较值低寄存器(ADC1CVL)       |     |

| 14.4.7 配置寄存器(ADC1CFG)         |     |

| 14.4.8 引脚控制 1 寄存器(APCTL1)     |     |

| 14.4.9 引脚控制 2 寄存器(APCTL2)     | 189 |

| 14.4.10 引脚控制 3 寄存器(APCTL3)    | 189 |

| 14.5 功能描述                     | 190 |

| 14.5.1 时钟选择和分频控制              | 190 |

| 14.5.2 输入选择和引脚控制              | 191 |

| 14.5.3 硬件触发                   | 191 |

| 14.5.4 转换控制                   | 191 |

| 14.5.4.1 初始化转换                | 191 |

| 14.5.4.2 完成转换                 | 191 |

| 14.5.4.3 终止转换                 | 191 |

| 14.5.4.4 电源控制                 |     |

| 14.5.4.5 总转换时间                |     |

| 14.5.5 自动比较功能                 |     |

| 14.5.6 MCU 等待模式操作             |     |

| 14.5.7 MCU stop3 模式操作         |     |

| 14.5.7.1 禁止 ADACK 的 stop3 模式  |     |

| 14.5.7.2 允许 ADACK 的 stop3 模式  |     |

| 14.5.8 MCU stop1 和 stop2 模式操作 |     |

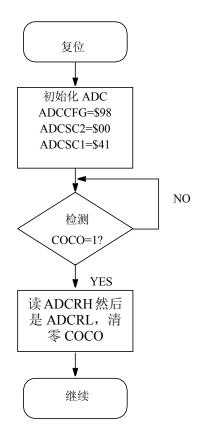

| 14.6 初始化信息                    |     |

| 14.6.1 ADC 模块初始化举例            |     |

| 14.6.1.1 初始化顺序                | 194 |

| 14.6.1.2 伪代码举例                | 194 |

| 14.7 应用信息                     |     |

| 14.7.1 外部引脚和安排                |     |

| 14.7.1.1 模拟电源引脚               |     |

| 14.7.1.2 模拟参考引脚               |     |

| 14.7.1.3 模拟输入引脚               |     |

| 14.7.2 错误源                    |     |

| 14.7.2.1 采样错误                 |     |

| 14.7.2.2 引脚泄露误差               |     |

| 14.7.2.3 噪音错误                 |     |

| 14.7.2.4 编码宽度和量化误差            |     |

| 14.7.2.5 线性误差                 |     |

| 14.7.2.6 编码抖动、非单调性和遗编码        |     |

|                               |     |

| 十五章 开发支持                      | 199 |

| 15.1 简介                       | 199 |

| 15.1.1 特征                     |     |

| 15.2 背景调是控制器                  | 200 |

| 15.2.1 BKGD 引脚描述                 |     |

|----------------------------------|-----|

| 15.2.2 通信细节                      | 201 |

| 15.2.3 BDC 命令                    |     |

| 15.2.4 BDC 硬件断点                  | 204 |

| 15.3 片上调试系统(DBG)                 |     |

| 15.3.1 比较器 A 和 B                 | 204 |

| 15.3.2 总线信息捕捉和 FIFO 操作           | 205 |

| 15.3.3 流程改变信息                    | 205 |

| 15.3.4 标记与强制断点和触发器               | 206 |

| 15.3.5 触发模式                      | 206 |

| 15.3.6 硬件断点                      | 207 |

| 15.4 寄存器定义                       | 208 |

| 15.4.1 BDC 寄存器和控制位               | 208 |

| 15.4.1.1 BDC 状态和控制寄存器(BDCSCR)    | 208 |

| 15.4.1.2 BDC 断点匹配寄存器(BDCBKPT)    | 209 |

| 15.4.2 系统背景调试强制复位寄存器(SBDFR)      | 210 |

| 15.4.3 DBG 寄存器和控制位               | 210 |

| 15.4.3.1 调试比较器 A 的高地址页寄存(DBGCAH) | 210 |

| 15.4.3.2 调试比较器 A 的低位寄存器(DBGCAL)  | 210 |

| 15.4.3.3 调试比较器 B 的高地址页寄存(DBGCAH) | 210 |

| 15.4.3.4 调试比较器 B 的低位寄存器(DBGCAL)  | 210 |

| 15.4.3.5 调试 FIFO 高地址页寄存器(DBGFH)  | 210 |

| 15.4.3.6 调试 FIFO 低位寄存器(DBGFL)    | 211 |

| 15.4.3.7 调试控制寄存器(DBGC)           | 211 |

| 15.4.3.8 调试触发寄存器(DBGT)           | 212 |

| 15.4.3.9 调试状态寄存器(DBGS)           | 212 |

| 附录 A 电气特性和时序规范                   | 214 |

| A.1 概述                           | 214 |

| A.2 参数分类                         | 214 |

| A.3 最大绝对额定值                      | 214 |

| A.4 热特性                          | 215 |

| A.5 ESD 保护和闭锁抗扰度                 | 216 |

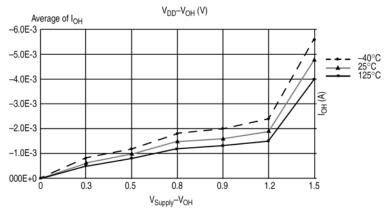

| A.6 DC 特性                        | 216 |

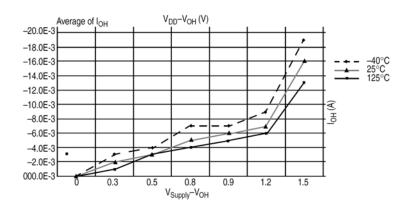

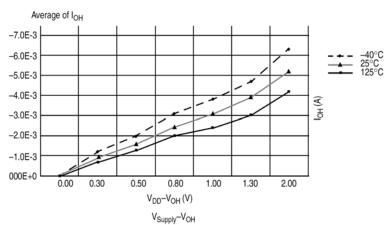

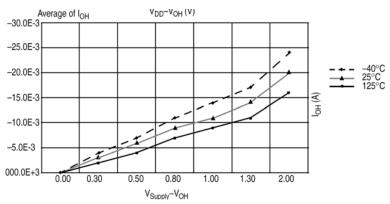

| A.7 电源电流特性                       | 219 |

| A.8 ADC 特性                       | 222 |

| A.9 内部时钟产生模块特性                   | 224 |

| A.9.1 ICG 频率规格                   | 225 |

| A.10 AC 特性                       | 227 |

| A.10.1 控制时序                      | 227 |

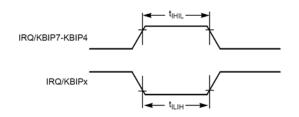

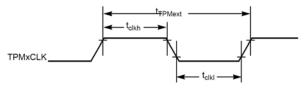

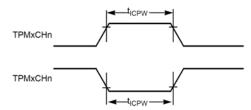

| A.10.2 定时器/PWM(TPM)模块时序          | 229 |

| A.11 SPI 特性                      | 229 |

| A.12 FLASH 规格                    | 232 |

| A.13 EMC 性能                      | 233 |

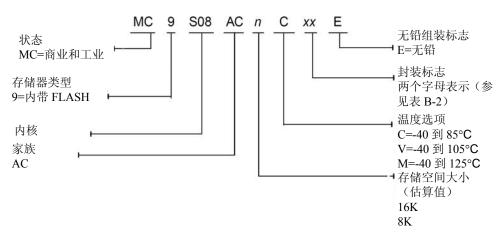

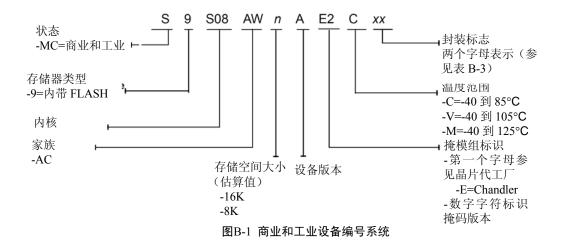

| 附录 B | 订购须知和机械制图 | 234 |

|------|-----------|-----|

| B.1  | 订购须知      | 234 |

|      | ) 机械组图    | 235 |

## 第一章 绪论

## 1.1 概述

MC9S08AC16 系列属于 8 位微控制单元(MCU),是高性能低功耗的 HCS08 家族中的成员。这个家族中的所有的 MCU 都使用 HCS08 核,并且可以使用多种模块、内存容量、内存类型和封装类型。

#### 注:

- 1. MC9S08AC16 和 MC9S08AC8 被规定使用在消费和工业的应用中。

- 2. S9S08AW16A 和 S9S08AW8A 被规定使用在汽车的应用中。

- 表 1-1 概括了在 MCU 中可用的特征集合。

表 1-1 MCU 的特征和封装

| 消费工业类的"AC"设备 |         |           |    |           |     |    |  |

|--------------|---------|-----------|----|-----------|-----|----|--|

| 特征           | N       | AC9S08AC1 | .6 | MC9S08AC8 |     |    |  |

| FLASH容量(字节)  |         | 16K       |    | 8K        |     |    |  |

| 内存容量 (字节)    |         | 1024      |    |           | 768 |    |  |

| 引脚数量         | 48      | 44        | 42 | 48        | 44  | 42 |  |

| ADC通道        | 8       | 8         | 6  | 8         | 8   | 6  |  |

| TPM1通道       | 4       | 4         | 2  | 4         | 4   | 2  |  |

| TPM2通道       | 2       | 2         | 2  | 2         | 2   | 2  |  |

| TPM3通道       | 2       | 2         | 2  | 2         | 2   | 2  |  |

| KBI引脚        | 7       | 6         | 4  | 7         | 6   | 4  |  |

| GPIO引脚       | 38      | 34        | 22 | 38        | 34  | 22 |  |

| 适用于消费工业领域    | yes yes |           |    |           |     |    |  |

| 适用于汽车领域      | no no   |           |    |           |     |    |  |

汽车类的"AW"设备

| 特征           | S  | 9S08AW16 | Mo | MC9S08AW8A |     |    |  |  |  |  |  |

|--------------|----|----------|----|------------|-----|----|--|--|--|--|--|

| FLASH容量 (字节) |    | 16K      |    |            | 8K  |    |  |  |  |  |  |

| 内存容量(字节)     |    | 1024     |    | 768        |     |    |  |  |  |  |  |

| 引脚数量         | 48 | 44       | 42 | 48         | 44  | 42 |  |  |  |  |  |

| ADC通道        | 8  | 8        | 6  | 8          | 8   | 6  |  |  |  |  |  |

| TPM1通道       | 4  | 4        | 2  | 4          | 4   | 2  |  |  |  |  |  |

| TPM2通道       | 2  | 2        | 2  | 2          | 2   | 2  |  |  |  |  |  |

| TPM3通道       | 1  | -        | -  | -          | -   | -  |  |  |  |  |  |

| KBI引脚        | 7  | 6        | 4  | 7          | 6   | 4  |  |  |  |  |  |

| GPIO引脚       | 38 | 34       | 22 | 38         | 34  | 22 |  |  |  |  |  |

| 适用于消费工业领域    |    | no       |    |            | no  |    |  |  |  |  |  |

| 适用于汽车领域      |    | yes      |    |            | yes |    |  |  |  |  |  |

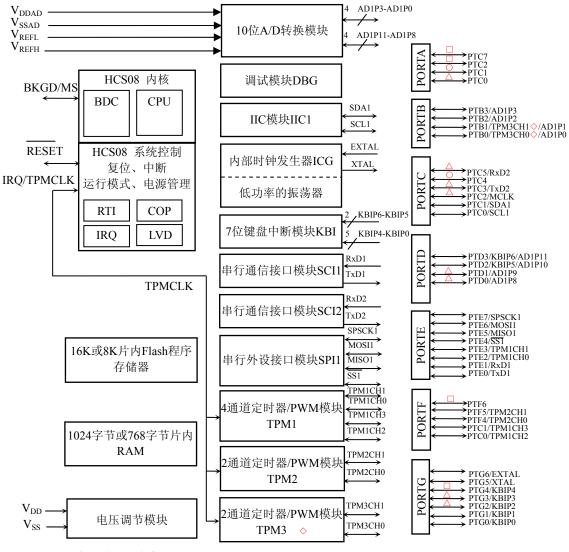

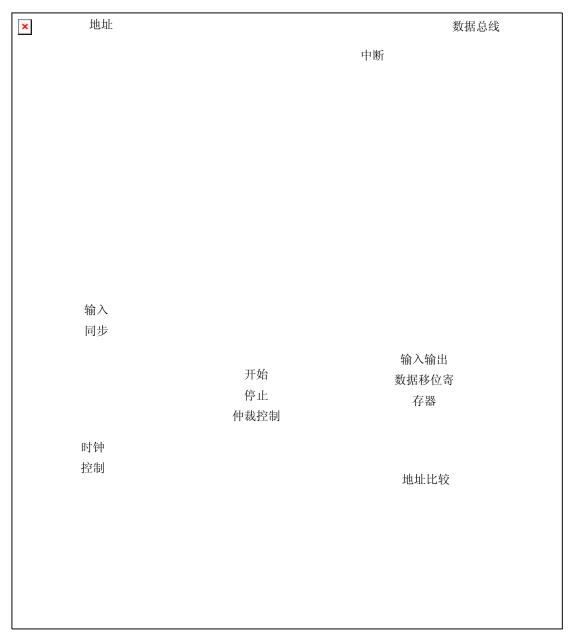

### 1.2 MCU结构框图

MC9S08AC16 系列 MCU 的结构框图如图 1-1 所示。

- □=在32或44引脚中不可用。

- ○=在32引脚的封装中不可用。

- △=在44引脚的封装中不可用。

- ◇=在S9S08AWxxA设备中不可用。

#### 注:

- 1. 端口引脚作为输入时可以通过软件设置选择内部上拉设备。

- 2. 若IRQ使能(IRQPE=1),引脚包括可软件配置的上下拉设备。若选择了上升沿检测(IRQEDG=1),下拉使能。

- 3. IRQ没有通过钳位二极管连向V<sub>DD</sub>。IRQ不能加载高于V<sub>DD</sub>的电平

- 4. 引脚包含集成的上拉设备。

- 5. PTD3、PTD2和PTG4引脚包含上拉/下拉设备。当KBI使能 (KBIPEn=1) 而且上升沿被选择(KBEDGn=1),下拉使能。

#### 图1-1 MC9S08AC16结构框图

表 1-2 列举了片上模块的版本。

表 1-2 片上模块版本

| 模块            | 版本 |

|---------------|----|

| 模数转换 (ADC)    | 1  |

| 内部时钟发生器 (ICG) | 4  |

| 内部 IC 总线(IIC) | 2  |

| 键盘中断 (KBI)    | 1  |

| 串行通信接口(SCI)   | 4  |

| 串行外设接口(SPI)  | 3 |

|--------------|---|

| 定时器脉宽调制(TPM) | 3 |

| 中央处理单元 (CPU) | 2 |

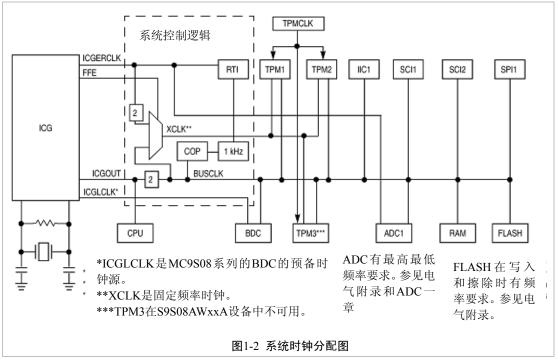

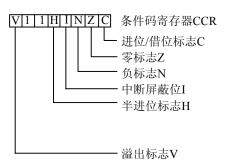

#### 1.3 系统时钟分配

MCU 内部的一些模块可以选择时钟脉冲源。图 1-2 表示了一个简化的时钟接线图。ICG 提供了时钟脉冲源:

- ICGOUT 是 ICG 模块的输出,它是下列各项中的一个:

- 外部的晶体振荡器

- ▶ 外部的时钟脉冲源

- 数控振荡器 (DCO) 在频率锁定环子模块中的输出

- ICG 内的控制位决定它连在哪个源上

- FFE 是在 ICG 里面产生的一个控制信号。如果 ICGOUT 的频率>4\*(ICGERCLK 的频率,该信号为逻辑 1,固定频率的时钟信号是 ICGERCLK/2。否则固定频率的时钟信号是 BUSCLK

- ICGLCLK——在总线时钟比较慢的系统中,开发工具可以选择内部自发生时钟源(~8MHz)来加速系统的 BDC 通信

- ICGERCLK——外部引用时钟可以作为实时中断的时钟源,也可以作为 ADC 模块的 AKTCKL 的输入

## 第二章 引脚及其连接

## 2.1 简介

本章描述了连接到封装引脚上的信号,包括一张管脚图,一张信号表和信号的具体描述。

### 2.2 设备的管脚分配

图 2-1 表示了 MC9S08AC16 系列设备的 48 引脚 QFN 引脚排列。

图 2-2 中显示了 MC9S08AC16 系列设备的 44 引脚 LQFP 引脚排列。

1. TPM3 在 S9S08AwxxA 中不可用。

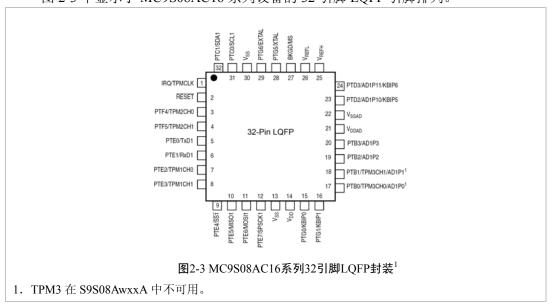

图 2-3 中显示了 MC9S08AC16 系列设备的 32 引脚 LQFP 引脚排列。

表 2-1 各封装的可用引脚

| ī  | 引脚与 |    |          | 最高      | Ē      | 引脚号 | <u>1</u> | 最低 优先级 最高 |          |                      |       |

|----|-----|----|----------|---------|--------|-----|----------|-----------|----------|----------------------|-------|

| 48 | 44  | 32 | 端口引<br>脚 | 高1      | 高2     | 48  | 44       | 32        | 端口引<br>脚 | 高1                   | 高2    |

| 1  | 1   | _  | PTC4     |         |        | 25  | _        | _         | PTA7     |                      |       |

| 2  | 2   | 1  |          | IRQ     | TPMCLK | 26  | 23       | 17        | PTB0     | TPM3CH0 <sup>1</sup> | AD1P0 |

| 3  | 3   | 2  |          |         | RESET  | 27  | 24       | 18        | PTB1     | TPM3CH1 <sup>1</sup> | AD1P1 |

| 4  | 4   | _  | PTF0     | TPM1CH2 |        | 28  | 25       | 19        | PTB2     | AD1P2                |       |

| 5  | 5   | _  | PTF1     | ТРМ1СН3 |        | 29  | 26       | 20        | PTB3     | AD1P3                |       |

| 6  | 6   | 3  | PTF4     | ТРМ2СН0 |        | 30  | 27       | _         | PTD0     | AD1P8                |       |

| 7  | 7  | 4  | PTF5 | TPM2CH1 |        | 31 | 28 | _  | PTD1 | AD1P9  |                     |

|----|----|----|------|---------|--------|----|----|----|------|--------|---------------------|

| 8  |    | _  | PTF6 |         |        | 32 | 29 | 21 |      |        | $V_{\mathrm{DDAD}}$ |

| 9  | 8  | 5  | PTE0 |         | TxD1   | 33 | 30 | 22 |      |        | V <sub>SSAD</sub>   |

| 10 | 9  | 6  | PTE1 |         | RxD1   | 34 | 31 | 23 | PTD2 | AD1P10 | KBIP5               |

| 11 | 10 | 7  | PTE2 | TPM1CH0 |        | 35 | 32 | 24 | PTD3 | AD1P11 | KBIP6               |

| 12 | 11 | 8  | PTE3 | TPM1CH1 |        | 36 | 33 | _  | PTG3 |        | KBIP3               |

| 13 | 12 | 9  | PTE4 |         | SS1    | 37 | _  | _  | PTG4 | KBIP4  |                     |

| 14 | 13 | 10 | PTE5 |         | MISO1  | 38 | 34 | 25 |      |        | $V_{REFH}$          |

| 15 | 14 | 11 | PTE6 |         | MOSI1  | 39 | 35 | 26 |      |        | $V_{REFL}$          |

| 16 | 15 | 12 | PTE7 |         | SPSCK1 | 40 | 36 | 27 | BKGD | MS     |                     |

| 17 | 16 | 13 |      |         | VSS    | 41 | 37 | 28 | PTG5 | XTAL   |                     |

| 18 | 17 | 14 |      |         | VDD    | 42 | 38 | 29 | PTG6 | EXTAL  |                     |

| 19 | 18 | 15 | PTG0 |         | KBIP0  | 43 | 39 | 30 |      |        | V <sub>SS</sub>     |

| 20 | 19 | 16 | PTG1 |         | KBIP1  | 44 | 40 | 31 | PTC0 |        | SCL1                |

| 21 | 20 |    | PTG2 |         | KBIP2  | 45 | 41 | 32 | PTC1 |        | SDA1                |

| 22 | 21 |    | PTA0 |         |        | 46 | 42 | —  | PTC2 |        | MCLK                |

| 23 | 22 | _  | PTA1 |         |        | 47 | 43 | —  | PTC3 |        | TxD2                |

| 24 | _  | _  | PTA2 |         |        | 48 | 44 |    | PTC5 |        | RxD2                |

<sup>1.</sup> TPM3在S9S08AwxxA中不可用。

表 2-2 引脚功能参考

| 信号功能    | 举例                           | 参考              |

|---------|------------------------------|-----------------|

| 端口引脚    | PTAx, PTBx                   | 第6章"并行输入输出"     |

| SPI     | SS、MISO、MOSI、SPSCK           | 第12章 "SPI"      |

| 键盘中断    | KBIPx                        | 第9章"键盘中断"       |

| 定时器/PWM | TCLK、TPMCHx                  | 第10章 "定时器/PWM   |

| IIC     | SCL, SDA                     | 第13章"内部集成电路"    |

| 内部集成电路  | TxD、RxD                      | 第11章"串行通信接口"    |

| 串行通信接口  | EXTAL, XTAL                  | 第8章"内部时钟发生器"    |

| 晶振/时钟   | ADPx                         | 第14章 "AD转换转换器"  |

| 电源/核    | BKGD/MS, $V_{DD}$ , $V_{SS}$ | 第2章 "引脚和连接"     |

| 复位和中断   | RESET、IRQ                    | 第5章"复位,中断和系统配置" |

## 2.3 推荐的系统连接

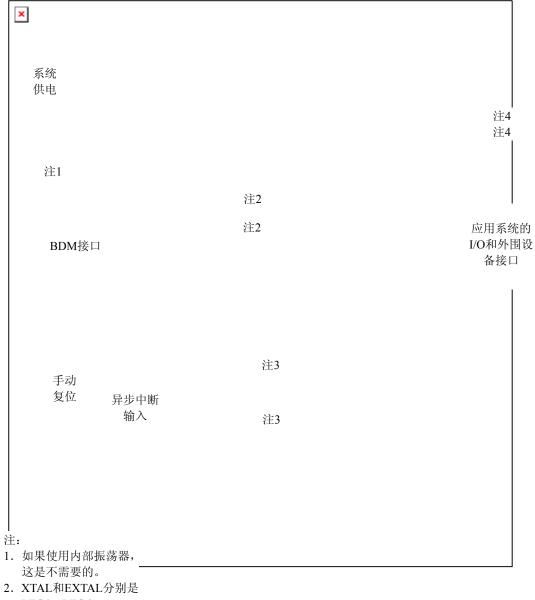

图 2-1 显示了几乎所有 MC9S08AC16 系列应用系统最典型的引脚连接。

- PTG5、PTG6。 3. 在电磁兼容性应用中,

- 推荐将RESET和ISR接 上RC过滤器。

- 4. TPM3在S9S08AWxxA 中不可用。

图2-4 基本系统连接

下面将详细介绍系统连接。

## 2.3.1 电源(V<sub>DD</sub>、2×V<sub>SS</sub>、V<sub>DDAD</sub>和V<sub>SSAD</sub>)

$V_{DD}$ 和  $V_{SS}$ 是 MCU 的主要供电引脚。该电压源对所有的输入/输出(I/O)缓冲电路和内部电压调节器供电。内部电压调节器向 CPU 和其他 MCU 内部电路提供稳定的低压源。

通常应用系统有两个单独的电容器和电源引脚相连。一个大容量电解电容器,如 10uF 的钽电容,用来为全体系统提供大电量存储,和一个  $0.1 \mu F$  的陶瓷旁路电容,尽可能的靠近 MCU 电源引脚  $V_{DD}$  和  $V_{SS}$ ,用以抑制高频噪声。MC9S08AC16 还有一个次要  $V_{SS}$  引脚。这个引脚连接到系统地或经过一个低阻抗连接到主要的  $V_{SS}$  引脚。

$V_{DDAD}$  和  $V_{SSAD}$  也是 MCU 的电源引脚。该电压源给 ADC 模块提供电源。一个  $0.1\,\mu$  F 的陶瓷旁路电容应尽可能靠近 MCU 的这两个电源引脚,用来抑制高频噪声。

#### 2.3.2 振荡器(XTAL与EXTAL)

复位 MCU 时使用内部产生的频率(自发生时钟模式)相当于 8MHz 晶体频率。这个频率源在复位启动时使用,也可以作为时钟源以避免长时间的晶体启动延时。MCU 也包含了一个内部时钟产生器(ICG)模块,这个模块用来启动 MCU。关于 ICG 的更多信息参考第八章"内部时钟产生器(S08ICGV4)"。

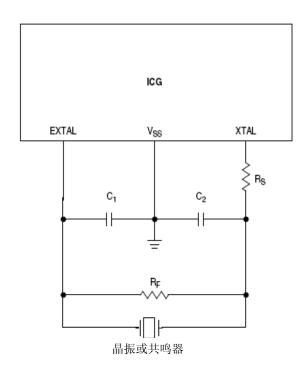

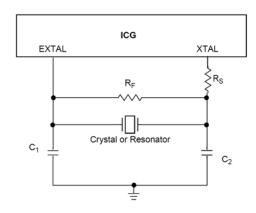

MCU 中的振荡器为传统的皮尔斯振荡器,它可容纳一个晶体或陶瓷谐振器,其频率范围可通过 ICGC1 寄存器中的 RANGE 位在两个频率范围里进行选择。除了晶体或陶瓷谐振器,外部振荡器也能和 EXTAL 输入引脚相连,但 XTAL 输出引脚必须悬空。

下面的讨论将参考图 2-4。 $R_S$ (如果使用)和  $R_F$  应该是低电感的电阻,如碳合成物电阻。绕线电阻和一些金属薄膜电阻有很大的电感值。C1 和 C2 应该是为高频应用专门设计的高品质陶瓷电容。

$R_F$  在晶振启动时被用来提供一个偏压电路以保持 EXTAL 输入在其线性范围内,它的值通常不是关键的。典型的系统使用 1 M  $\Omega$  到 10 M  $\Omega$  。高值对湿度敏感,低值减小增益(在特殊情况下)可以阻止启动。

C1 和 C2 通常在 5pF 到 25pF 的范围内,并按照要求和特定的晶体和谐振器相匹配。在给 C1 和 C2 选定大小时一定要考虑到 PCB 板电容和 MCU 引脚电容。晶体制造商通常指定一个负载电容,该电容值应等于 C1 和 C2 的串联值,C1 和 C2 一般选用同样大小的电容。作为首选的近似值,为每个振荡器引脚(EXTAL 和 XTAL)使用约 10pF 的电容作为引脚和 PCB 的连接电容。

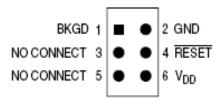

### 2.3.3 复位

复位引脚是一个有上拉电阻的专用引脚。它有输入滞后,一个大的电流输出驱动,没有输出摆率控制。因为有内部上电复位和低压复位电路,所以通常不需要外部的复位电路。这个引脚通常连接到标准 6 引脚的背景调试连接器上,这样开发系统能够直接复位 MCU系统。如果需要,可以通过附加一个简单的接地开关手动复位(下拉复位引脚强制复位)。

每当有复位产生(无论来自外部信号还是来自内部系统),复位引脚被拉低约 34 总线周期。复位电路解析复位的原因并且在复位状态寄存器(SRS)中设置相应的位。

在对 EMC 敏感的应用中,在复位引脚上推荐一个外部的 RC 过滤器。参见图 2-4 的例子。

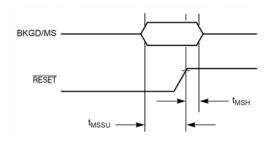

### 2.3.4 背景/模式选择(BKGD/MS)

在复位时,背景/模式选择(BKGD/MS) 引脚的功能是模式选择。在复位升起后,这个引脚立即变为背景脚,可用作背景调试。作为背景/模式选择引脚时,这个引脚包括一个内部上拉设备,输入滞后,一个标准的输出驱动和无输出摆率控制。

若这个引脚没有连接,则 MCU 在复位的上升沿进入正常的操作模式。如果调试系统被连接到 6 引脚的标准背景调试接口,它可以在复位上升沿时保持 BKGD/MS 为低,强制 MCU 进入背景模式。

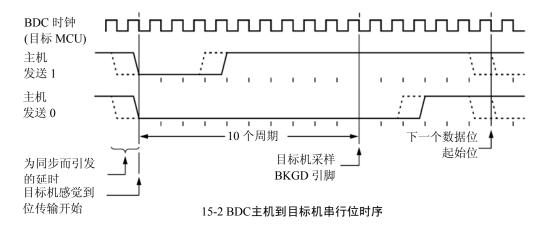

BKGD 引脚主要被背景调试控制器(BDC)使用,它使用约定好的协议进行通信,该协议使用目标 MCU 的 16 个 BDC 时钟周期来传送每一位。目标 MCU 的 BDC 时钟频率可以

和总线时钟频率一样快,因此不要将任何大的电容和 BKGD/MS 引脚相连,那会干扰背景串行通信。

虽然 BKGD 引脚是一个伪开漏引脚,但是背景调试通信协议提供了简短的,主动驱动,高加速脉冲以确保快速上升时间。电缆上的小电容和内部上拉设备的绝对值对判断 BKGD 引脚上上升和下降时间几乎不起任何作用。

#### 2.3.5 ADC参考引脚(V<sub>REFH</sub>与V<sub>REFL</sub>)

V<sub>REFH</sub> 和 V<sub>REFL</sub> 分别对应输入到 ADC 模块的参考高电压和参考低电压。

#### 2.3.6 外部的中断引脚(IRQ)

IRQ 引脚既是 IRQ 中断的输入源也是 BIH 和 BIL 指令的输入。如果中断请求函数未允许,这个引脚不会产生任何作用。

在对 EMC 敏感的应用中,在复位引脚上推荐一个外部的 RC 过滤器。参见图 2-4 的例子。

### 2.3.7 通用I/O及外设端口

其他的引脚分配给通用 I/O 和片上的外围功能,例如定时器和串行 I/O 系统。一旦复位,所有这些引脚都设定为高阻通用输入口,内部上拉设备无效。

注:

为了避免来自浮动输入引脚上的额外的电流消耗,应用程序中的复位初始化程序应使能片上上 拉设备或将闲置引脚的方向改变为输出,使引脚不浮动。

有关使用这些引脚作为通用 I/O 引脚的信息,参考第六章"并行输入输出"。或者有关 片上外设系统如何以及何时用这些引脚的信息,请参考表 2-2 中适当的章节。

当一个片上外设系统使用一个引脚时,即使外设模块通过控制引脚输出缓冲使能来控制引脚方向,但是数据方向控制位仍决定从端口数据寄存器读出的是什么。参考第六章"并行输入输出"有更多信息。

只要引脚作为输入,即使这些引脚被片上外设模块控制,但是它们的上拉使能位仍然可以控制这些引脚是否有片上的上拉设备。当 PTD3,PTD3 和 PTG4 引脚被 KBI 模块控制并且被设定为上升沿/高电平敏感时,上拉使能控制位使能下拉设备而不是上拉设备。相似的,当 IRQ 作为 IRQ 引脚而且被规定为检测上升沿,上拉使能控制位使能下拉设备而不是使能上拉设备。

注意:

当一个可选的功能第一次被使能时,模块可能会得到一个伪边。用户软件应该在中断使能前清除任何相关的标志位。当多个模块被使能,表 2-1 说明了优先级关系。最高优先级的模块将会控制引脚。在引脚上有一个较低优先级的功能下,选择这个引脚更高优先级的功能会产生伪边给较低优先级模块。建议在使能另一个模块前所有的模块共享一个无效的引脚。

## 第三章 工作模式

### 3.1 简介

本章讲述了 MC9S08AC16 系列的工作模式,并描述了如何进入和退出各个模式及各个模式的功能。

#### 3.2 特征

- 普通用户在运行模式下操作

- 等待模式:

- CPU 关闭以节能

- 系统时钟仍然运行

- 维持完全的电压稳压

- 停止模式:

- 系统时钟停止; 电压调节器待命

- 停止 2: 内部电路的部分断电, RAM 内容保留

- 停止3: 所有内部电路供电,以快速恢复

#### 3.3 运行模式

这是 MC9S08AC16 的正常操作模式。当 BKGD/MS 在复位的上升沿时是高电平,此模式被选择。在此模式下复位之后,CPU 从存储器中的\$FFFE:\$FFFF 处取出程序执行的起始地址,执行内存中的代码。

### 3.4 背景调试模式

背景调试模式的功能由 HCS08 核中的背景调试控制器(BDC, Background Debug Controller)管理。BDC 和片上调试模块(DBG)一起,提供了在软件运行时分析 MCU 的操作的方法。

可通过以下五种方式进入背景调试模式:

- BKGD/MS 引脚在复位的上升沿时是低电平

- 从 BKGD 引脚接收到 BACKGROUND 命令

- 当执行 BGND 指令时

- 当遇到 BDC 断点时

- 当遇到 DBG 断点时

进入背景调试模式后,CPU 被置于挂起状态,等待串行背景命令而不是执行用户应用程序的指令。

背景命令有两种类型:

● 非插入命令,定义为可在用户程序运行时发出的指令。当 MCU 在运行模式下时, 非插入命令可经由 BKGD 引脚发出。当 MCU 在背景调试模式下也可执行非插入 命令。非插入命令包括:

- 存储器访问命令

- 存储器访问状态命令

- BDC 寄存器访问命令

- BACKGROUND 命令

- 背景命令,只有当 MCU 在背景调试模式下才可以执行。背景命令包括以下命令:

- 读写 CPU 寄存器

- 单步调试指令

- 离开背景调试模式,返回用户应用程序(GO)

背景调试模式通常用于在 MCU 第一次在运行模式下运行之前向 FLASH 存储器写入一个引导程序或者用户应用程序。当 MC9S08AC16 从 Freescale 出厂时,除非特别指明,FLASH 存储器默认为擦除的,在 FLASH 存储器初次编程之前,由于 FLASH 存储器中没有程序,因此在运行模式下没有程序可以运行。背景调试模式也可用于在 FLASH 存储器已经写入程序后擦除和重新写入程序。

更多有关背景调试模式的信息可见第十五章开发支持部分。

#### 3.5 等待模式

执行到 WAIT 指令时,即可进入等待模式。在执行 WAIT 指令后,CPU 进入没有时钟的低功耗状态。当 CPU 进入等待模式时,CCR 寄存器里面的 I 位将被清零并允许中断。当有中断请求发生,CPU 就会脱离等待模式,继续正常处理,从相应的中断服务程序栈操作开始运行。

在等待模式下,有些些背景调试命令的使用限制,只有 BACKGROUND 命令和存储器 访问状态命令可用。虽然存储器访问状态命令不允许访问存储器,但是它会报出错误来说明 MCU 在停止模式或等待模式。BACKGROUND 命令可用于使 MCU 从等待模式唤醒进入背景调试模式。

### 3.6 停止模式

在系统选择寄存器中的 STOPE 位置位时,当执行到一个 STOP 指令就进入了两种停止模式中的一种。在这两种停止模式中,所有的内部时钟被停止。如果 STOPE 位在 CPU 执行 STOP 指令时没有置位,MCU 将不会进入任何停止模式,并强制产生一个非法指令复位。可以通过设置 SPMSC2 里的相应标志位来选择进入哪种停止模式。

HCS08 设备被设计成低压操作(1.8V 到 3.6V),也包括停止 1 模式。MC9S08AC16 系列设备不包括停止 1 模式。

表 3-1 总结了 MCU 在每种停止模式下的行为。

CPU, 数字外 时钟 电压调 PPDC 模式 RAM ADC I/O RTI 设, FLASH 模块 节器 STOP2 关 关 不可用 维持状态 1 待命 待命 可选开 关<sup>1</sup> STOP3 0 待命 可选开 待命 维持状态 可选开 待命

表 3-1 停止模式下的行为

<sup>(1)</sup> STOP3模式下晶振可以设置为运行,参见ICG寄存器。

### 3.6.1 Stop2模式

STOP2 模式提供非常低的待命电压能保持 RAM 内容和所有 I/O 端口状态的待命功耗。 为了进入 STOP2 模式,在执行 STOP 指令前必须选择停止 2 模式 (PPDC=1) 和使能停止模式 (STOPE=1)。另外, LVD 在停止模式 (LVDSE=LVDE=1) 下不能操作。如果 LVD 在停止模式下使能,不管 PPDC 的状态是什么, MCU 在执行 STOP 指令后都会进入停止 3 模式。

进入 STOP2 模式之前,用户可以在 RAM 中保存 I/O 口寄存器的内容,和其它想在退出 STOP2 模式后恢复的寄存器的内容。在离开 STOP2 模式后,这些内容可在闭锁的端口开放 之前被用户软件恢复。

当 MCU 处于 STOP2 模式下时,所有由电压调节器供电的内部电路都是关闭的,除了 RAM。电压调节器处于低功耗待命状态,就像 ADC 模块一样。进入 STOP2 模式后,I/O 端口的状态被锁定。这些状态将在 STOP2 模式中被保持,直到在退出 STOP2 模式后 SPMSC2 寄存器中的 PPDACK 标志位被写 1。

通过 MCU 的唤醒端口(RESET或者 IRQ/TPMCLK)或者 RTI 中断可离开 STOP2 模式。不管在进入 STOP2 之前 IRQ/TPMCLK 是如何设置的,它在 STOP2 模式下总是低电平输入有效。

当从 STOP2 模式中被唤醒后,MCU 将以类似上电复位(POR)的方式启动,但是端口状态仍然保持锁定。CPU 将取复位向量。系统和所有外设将处于它们的默认复位状态,且必须被初始化。

从 STOP2 模式中唤醒之后 SPMSC2 寄存器中的 PPDF 标志位将置位。该标志位也许用于指示用户代码执行 STOP2 恢复程序。PPDF 保持置位并且 I/O 端口状态保持闭锁,直到 SPMSC2 寄存器中的 PPDACK 标志位写 1。

为保持设置为通用 I/O 引脚的状态,在向 PPDACK 标志位写入之前,用户必须用存储在 RAM 中的 I/O 端口寄存器中的内容来恢复端口寄存器。如果在写入 PPDACK 之前,没有从 RAM 恢复端口寄存器,当 I/O 端口闭锁打开时,寄存器中的内容将是它们的复位默认状态的值,I/O 端口转换成复位状态。

对于设置为外设 I/O 口的引脚,在向 PPDACK 标志位写入之前,用户必须重新配置外设模块的接口引脚。如果在写入 PPDACK 之前,外设模块不可用,当 I/O 端口闭锁打开时,引脚将被它们的相关端口控制寄存器控制。

### 3.6.2 Stop3模式

为了进入 STOP3 模式,在执行 STOP 指令前必须选择停止 3 模式 (PPDC=1) 和使能停止模式 (STOPE=1)。进入 STOP3 模式后,所有 MCU 的时钟、包括振荡器本身都停止了。时钟模块(ICG),电压调节器和 ADC 都在待命状态。所有内部寄存器和逻辑,也包括 RAM 的内容都被保持。I/O 端口的状态不像 STOP2 模式中一样被锁定。取而代之的是,使用内部逻辑的状态控制需要保持的引脚的特点来保持它们的状态。

退出 STOP3 模式的方法有:复位RESET,或者一个由实时中断(RTI),LVD 系统,ADC,IRQ,KBI或 SCI产生的中断。

如果通过**RESET**退出 STOP3 模式,MCU 将复位,并从复位向量处执行。如果通过异步中断或实时中断退出,MCU 将从相应的中断向量处执行。

实时中断的单独时钟脉冲源(约等于 1KHz)允许在没有额外部件的情况下将 MCU 从 STOP2 或 STOP3 模式唤醒。当 RTIS2:RTIS1:RTIS0=0:0:0,实时中断功能和 1kHz 的时钟源不可用。当 1kHz 的时钟源不可用时,功耗更低,但此种情况下实时中断不可以将 MCU 从

STOP 模式中唤醒。

#### 3.6.3 停止模式下激活BDM使能

如果 BDCSCR 寄存器里的 ENBDM 标志位被置位,从运行模式进入背景调试模式是可能的。BDCSCR 寄存器将在第十五章开发支持部分介绍。如果当 CPU 执行 STOP 指令时,ENBDM 被置位,这样当 MCU 进入到停止模式后背景调试逻辑的系统时钟仍然在工作,所以背景调试的通信仍然是可以的。另外电压调节器没有进入低功耗待命状态,而是在满负荷工作中。如果用户尝试通过置 ENBDM 位进入 STOP2 模式,MCU 会进入到 STOP3 模式而不是 STOP1 或 STOP2 模式。

大部分背景命令在停止模式下不可用。存储器存取状态指令不允许存储器存取,但它们会报告一个错误标志,标志 MCU 在停止或等待模式。如果 ENBDM 置位,BACKGROUND 指令可以用于将 MCU 从停止模式中唤醒进入背景调试模式。一旦设备进入背景调试模式,所有背景命令都可用。表 3-2 总结了当背景调试模块使能时 MCU 在 STOP 模式下的行为。

| 模式    | PPDC | CPU, 数字外<br>设, FLASH | RAM | ICG | ADC | 电压调节<br>器 | I/O引脚 | RTI |

|-------|------|----------------------|-----|-----|-----|-----------|-------|-----|

| STOP3 | 任意   | 待命                   | 待命  | 活跃  | 不可用 | 活跃        | 状态保持  | 可选开 |

表 3-2 MCU 在启用背景调试模块的 STOP 模式下的行为

#### 3.6.4 停止模式下LVD使能

当供应电压下降到 LVD 电压值以下时,LVD 系统能够产生中断或复位。当 CPU 执行到 STOP 指令时,如果此时已经通过置 SPMSC1 寄存器中的 LVDE 和 LVDSE 位使得 LVD 有效,则在停止模式下电压调节器仍然保持工作。当 LVD 可用时(LVDSE=1),用户尝试进入 STOP2 模式,MCU 会进入到 STOP3 模式而不是 STOP1 或 STOP2 模式。表格 3-3 总结了在 LVD 使能时 MCU 在 STOP 模式下的行为。

| 模式    | PPDC | CPU、数字外<br>设、FLASH | RAM | ICG | ADC | 电压调<br>节器 | I/O  | RTI |

|-------|------|--------------------|-----|-----|-----|-----------|------|-----|

| STOP3 | 任意   | 待命                 | 待命  | 关闭  | 可选开 | 活跃        | 状态保持 | 可选开 |

表 3-3 MCU 在启用 LVD 的 STOP 模式下的行为

## 3.6.5 停止模式下的片上外设模块

当 MCU 进入任何停止模式,内部外设模块的系统时钟会停止。即使在例外情况下 (ENBDM=1),背景调试逻辑的时钟继续工作,外设的时钟也被停止以减少功耗。见 3.6.2 STOP3 模式以获得停止模式下系统行为的更多信息。

#### I/O 引脚:

- 当 MCU 在 STOP3 模式下, 所有 I/O 端口状态保持不变。

- 如果 MCU 配置为进入 STOP2 模式,所有 I/O 端口状态在进入停止模式前锁定。 存储器:

- 所有 RAM 和寄存器内容在 STOP3 模式下都是被保存的。

- 从 STOP2 模式下唤醒后,所有寄存器都将复位,但 RAM 内容保存,端口状态保持锁定直到 PPDACK 位被写入。用户可以在进入 STOP2 模式之前,将寄存器的内容保存在 RAM 中,并在离开 STOP2 模式后恢复这些数据。

- FLASH 的内容是非易失的,在任何停止模式下都会保存。

- ICG——在 STOP3 模式下,ICG 进入低功耗待命状态。当 ICG 在待命状态时,通过设置适当的控制位(OSCSTEN),振荡器可以保持工作。在 STOP2 模式下,ICG 是关闭的。即使 OSCSTEN 使能,振荡器也不能在 STOP2 下工作。MCU 从 STOP2 模式退出时从停止模式中唤醒,TPM 模块被复位并且必须被重新初始化。

- TPM——当 MCU 进入停止模式时,TPM1 和 TPM2 模块的时钟停止。模块停止工作。如果 MCU 配置成进入 STOP2 模式,当从停止模式唤醒以后 TPM 模块被复位并且必须被重新初始化。

- **ADC**——当 MCU 进入停止模式时,除非异步时钟源,ADACK 无效,否则 ADC 将进入低功耗待命状态。如果 MCU 配置为进入 STOP2,当从停止模式唤醒以后 ADC 模块被复位并且必须被重新初始化。

- **KBI**——在 STOP3 模式中,KBI 引脚仍然可用,并且作为一个中断源可以将 MCU 从 STOP3 模式唤醒。KBI 在 STOP2 中不可用,当从 STOP 模式中唤醒时,KBI 不能使用必须 重新初始化。

- SCI——当 MCU 进入停止模式时, SCI1 和 SCI2 的时钟停止。模块停止操作。如果 MCU 配置为进入 STOP2 或者 STOP1 模式, 当从停止模式唤醒以后 SCI 模块被复位并且必须被重新初始化。

- **SPI**—当 MCU 进入停止模式时,SPI 的时钟停止。模块停止操作。如果 MCU 配置为进入 STOP2 模式,当从停止模式唤醒以后 SPI 模块被复位并且必须被重新初始化。

- IIC——当 MCU 进入停止模式时,IIC 的时钟停止。模块停止操作。如果 MCU 配置为进入 STOP2 模式,当从停止模式唤醒以后 IIC 模块被复位并且必须被重新初始化。

- 电压调节器——当 MCU 进入任何停止模式时,电压调节器将进入低功耗待命状态,除非 LVD 在停止模式下使能或者 BDM 使能。

## 第四章 片上存储器

### 4.1 简介MC9SAC16系列存储映像

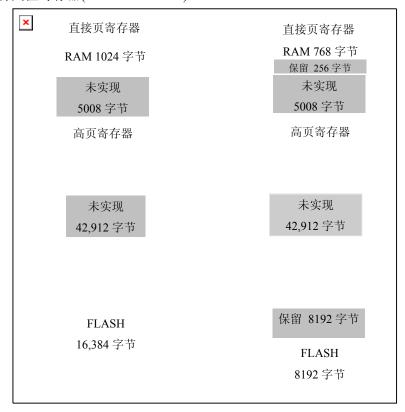

图 4-1 描述了 MC9S08AC16 系列 MCU 的存储映像,MC9S08AC16 的片上存储器由RAM、非易失的FLASH 存储器、输入/输出和控制/状态寄存器组成。

这些寄存器分成三组:

- 直接页寄存器(0x0000-0x006F)

- 高地址页寄存器(0x1800-0x185F)

- 非易失性寄存器(0xFFB0-0xFFBF)

图 4-1 MC9S08AC16 系列内存映像

## 4.1.1 复位和中断向量分配

表 4-1 描述了复位与中断向量的地址分配,至于其他 HCS08 系列 MCU 的向量名字和地址分配,请参考相关的数据手册。表中所示向量名是 Freescalse 公司提供的 MC9S08AC16 文档中给出的名字。有关复位、中断、中断优先权和中断屏蔽控制的详细信息,请参阅第5章复位和中断。

地址(高/低) 向量 向量名称 0xFFC0:FFC1 不用的向量空间 (可用于用户程序) 0xFFC4:FFC5 TPM3<sup>1</sup>溢出 0xFFC6:FFC7 Vtpm3ovf 0xFFC8:FFC9 TPM3<sup>1</sup>通道1 Vtpm3ch1 TPM3<sup>1</sup>通道0 0xFFCA:FFCB Vtpm3ch0 Vrti 0xFFCC:FFCD RTI1 Viic1 0xFFCE:FFCF IIC1 ADC1模数转换 Vadc1 0xffD0:FFD1 Vkeyboard1 0xFFD2:FFD3 **KBI** 0xFFD4:FFD5 SCI2发送 Vsci2tx 0xFFD6:FFD7 SCI2接收 Vsci2rx 0xFFD8:FFD9 SCI2错误 Vsci2err 0xFFDA:FFDB SCI1发送 Vsci1tx 0xFFDC:FFDD SCI1接收 Vsci1rx 0xFFDE:FFDF SCI1错误 Vsci1err 0xFFE0:FFE1 SPI1 Vspi1 TPM2溢出 Vtpm2ovf 0xFFE2:FFE3 0xFFE4:FFE5 TPM2通道1 Vtpm2ch1 0xFFE6:FFE7 TPM2通道0 Vtpm2ch0 TPM1溢出 Vtpm1ovf 0xFFE8:FFE9 未使用 0xFFEA:FFEB 0xFFEC:FFED 未使用

TPM1通道3

TPM1通道2

TPM1通道1

TPM1通道0

**ICG**

低电压检测

IRO

SWI

RESET

Vtpm1ch3

Vtpm1ch2

Vtpm1ch1

Vtpm1ch0

Vicg

Vlvd

Virq

Vswi

Vreset

表 4-1 复位和中断向量表

(1) TPM3在S9S08AWxxA中不可以

### 4.2 寄存器地址和位分配

MC9S08AC16 系列中的寄存器分为以下三组:

0xFFEE:FFEF 0xFFF0:FFF1

0xFFF2:FFF3

0xFFF4:FFF5

0xFFF6:FFF7

0xFFF8:FFF9

0xFFFA:FFFB

0xFFFC:FFFD 0xFFFE:FFFF

- 直接页寄存器位于存储空间前 112 字节处,所以可由高效的直接寻址指令访问。

- 高地址页寄存器较少被使用,所以它们位于存储器的\$1800 地址之后,这样就可以在直接页中留出更多的空间给经常使用的寄存器和变量。

- 非易失性寄存器由FLASH存储器中位于\$FFB0 \$FFBF 地址处的16个位置组成。 非易失性寄存器的位置包括:

- 在复位时加载到工作寄存器的两个值。

- 用户可以使用一个8字节的密码取得加密存储器的使用访问权。

因为非易失性寄存器是存储在 FLASH 存储器中的,所以它必须像其他的 FLASH 存储器那样擦除和写入。

直接页寄存器可以被高效的直接寻址方式指令访问。位操作指令可用于访问直接页寄

存器中的任何一位。表 4-2 总结了所有用户可访问的直接页寄存器及其控制位。

表 4-2 中的寄存器可以使用比较高效的直接寻址方式访问,这种方式只需要地址的低位字节。因此,第一纵列中地址的低位字节用粗体字表示。表 4-3 和表 4-4 中,第一纵列中完整的地址用粗体字表示。表 4-2,表 4-3,表 4-4 中,第二纵列的寄存器的名称亦用粗体字表示,以与右边的字节名称区分。没有定义的字节单元格以阴影表示。有 0 的阴影单元格表示不使用的字节总是读作 0。有横线的阴影单元格表示不使用或保留的字节,可以读作 1 或 0。

表 4-2 直接页寄存器概述

|                 | N. 1. 22 1 21 |        |        | 2 直及外向 |        |        |        | 1      |        |

|-----------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 地址              | 寄存器名称         | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| \$0000          | PTAD          | PTAD7  | R      | R      | R      | R      | PTAD2  | PTAD1  | PTAD0  |

| \$0001          | PTADD         | PTADD7 | R      | R      | R      | R      | PTADD2 | PTADD1 | PTADD0 |

| \$0002          | PTBD          | R      | R      | R      | R      | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| \$0003          | PTBDD         | R      | R      | R      | R      | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| \$00 <b>04</b>  | PTCD          | 0      | R      | PTCD5  | PTCD4  | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| \$0005          | PTCDD         | 0      | R      | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| \$0006          | PTDD          | R      | R      | R      | R      | PTDD3  | PTDD2  | PTDD1  | PTDD0  |

| \$0007          | PTDDD         | R      | R      | R      | R      | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| \$0008          | PTED          | PTED7  | PTED6  | PTED5  | PTED4  | PTED3  | PTED2  | PTED1  | PTED0  |

| \$00 <b>09</b>  | PTEDD         | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| \$00 <b>0A</b>  | PTFD          | R      | PTFD6  | PTFD5  | PTFD4  | R      | R      | PTFD1  | PTFD0  |

| \$00 <b>0B</b>  | PTCDD         | R      | PTFDD6 | PTFDD5 | PTFDD4 | R      | R      | PTFDD1 | PTFDD0 |

| \$00 <b>0</b> C | PTGD          | 0      | PTGD6  | PTGD5  | PTGD4  | PTGD3  | PTGD2  | PTGD1  | PTGD0  |

| \$00 <b>0D</b>  | PTGDD         | 0      | PTGDD6 | PTGDD5 | PTGDD4 | PTGDD3 | PTGDD2 | PTGDD1 | PTGDD0 |

| \$00 <b>0E</b>  | 保留            |        |        |        |        |        |        |        |        |

| \$00 <b>0F</b>  | 保留            | _      | _      | _      | _      | _      | _      | _      | _      |

| \$0010          | ADC1SC1       | COCO   | AIEN   | ADCO   |        |        | ADCH   |        |        |

| \$0011          | ADC1SC2       | ADACT  | ADTRG  | ACFE   | ACFGT  | 0      | 0      | R      | R      |

| \$0012          | ADC1RH        | 0      | 0      | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| \$0013          | ADC1RL        | ADR7   | ADR6   | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| \$0014          | ADC1CVH       | 0      | 0      | 0      | 0      | 0      | 0      | ADCV9  | ADCV8  |

| \$0015          | ADC1CVL       | ADCV7  | ADCV6  | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| \$0016          | ADC1CFG       | ADLPC  | AD     |        | ADLSMP |        | DDE    | ADI    | CLK    |

| \$0017          | APCTL1        | ADPC7  | ADPC6  | ADPC5  | ADPC4  | ADPC3  | ADPC2  | ADPC1  | ADPC0  |

| \$0018          | APCTL2        | ADPC15 | ADPC14 | ADPC13 | ADPC12 | ADPC11 | ADPC10 | ADPC9  | ADPC8  |

| \$0019          | APCTL3        | ADPC23 | ADPC22 | ADPC21 | ADPC20 | ADPC19 | ADPC18 | ADPC17 | ADPC16 |

| \$00 <b>1A</b>  | 保留            | _      |        | _      |        |        |        | _      | _      |

| \$00 <b>1B</b>  | 保留            | _      |        |        | _      | _      | _      | _      | _      |

| \$001C          | IRQSC         | 0      | IRQPDD | IRQEDG | IRQPE  | IRQF   | 0      | IRQIE  | IRQMOD |

| \$00 <b>1D</b>  | 保留            | _      | _      | _      | _      | _      | _      | _      | _      |

| \$00 <b>1E</b>  | KBISC         | KBEDG7 | KBEDG6 | KBEDG5 | KBEDG4 | KBF    | KBACK  | KBIE   | KBIMOD |

| \$00 <b>1F</b>  | KBIPE         | KBIPE7 | KBIPE6 | KBIPE5 | KBIPE4 | KBIPE3 | KBIPE2 | KBIPE1 | KBIPE0 |

| \$00 <b>20</b>  | TPM1SC        | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| \$0021          | TPM1CNTH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| \$0022          | TPM1CNTL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| \$0023          | TPM1MODH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| \$0024          | TPM1MODL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| \$0025          | TPM1C0SC      | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| \$0026          | TPM1C0VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| \$0027          | TPM1C0VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| \$0028          | TPM1C1SC      | CH1F   | CH1IE  | MA1B   | MS1A   | ELS1B  | ELS1A  | 0      | 0      |

| \$00 <b>29</b>  | TPM1C1VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| \$00 <b>2A</b>  | TPM1C1VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| \$00 <b>2B</b>  | TPM1C2SC      | CH2F   | CH2IE  | MS2B   | ELS2B  | MS2A   | ELS2A  | 0      | 0      |

| \$00 <b>2</b> C                  | TPM1C2VH          | Bit 15      | 14         | 13          | 12           | 11       | 10       | 9         | Bit 8     |

|----------------------------------|-------------------|-------------|------------|-------------|--------------|----------|----------|-----------|-----------|

| \$00 <b>2D</b>                   | TPM1C2VL          | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

| \$00 <b>2E</b>                   | TPM1C3SC          | CH3F        | CH3IE      | MS3B        | MS3A         | ELS3B    | ELS3A    | 0         | 0         |

| \$00 <b>2F</b>                   | TPM1C3VH          | Bit 15      | 14         | 13          | 12           | 11       | 10       | 9         | Bit 8     |

| \$0030                           | TPM1C3VL          | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

| \$0031                           | 保留                | _           | _          | _           | _            | _        |          | _         | _         |

| \$0032                           | 保留                | _           | _          | _           | _            | _        |          | _         | _         |

| \$0033                           | 保留                |             |            |             |              |          |          |           |           |

| \$0034                           | 保留                | _           | _          | _           | _            | _        |          | _         |           |

| \$0035                           | 保留                | _           | _          | _           | _            | _        |          | _         |           |

| \$0036                           | 保留                | _           | _          | _           | _            | _        |          | _         | _         |

| \$0037                           | 保留                |             |            |             |              | GDD11    | GDD 10   | - CDDO    |           |

| \$0038                           | SCI1BDH           | LBKDIE      | RXEDGIE    | 0           | SBR12        | SBR11    | SBR10    | SBR9      | SBR8      |

| \$0039                           | SCI1BDL<br>SCI1C1 | SBR7        | SBR6       | SBR5        | SBR4         | SBR3     | SBR2     | SBR1      | SBR0      |

| \$00 <b>3A</b><br>0x00 <b>3B</b> | SCI1C1            | LOOPS       | SCISWAI    | RSRC        | M            | WAKE     | ILT      | PE        | PT        |

| 0x00 <b>3C</b>                   | SCI1C2<br>SCI1S1  | TIE<br>TDRE | TCIE<br>TC | RIE<br>RDRF | ILIE<br>IDLE | TE<br>OR | RE<br>NF | RWU<br>FE | SBK<br>PF |

| 0x00 <b>3D</b>                   | SCI1S1<br>SCI1S2  | LBKDIF      | RXEDGIF    | 0           | RXINV        | RWUID    | BRK13    | LBKDE     | RAF       |

| 0x00 <b>3E</b>                   | SCI1S2<br>SCI1C3  | R8          | T8         | TXDIR       | TXINV        | ORIE     | NEIE     | FEIE      | PEIE      |

| 0x003E                           | SCI1D             | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

| 0x00 <b>31</b>                   | SCI2BDH           | LBKDIE      | RXEDGIE    | 0           | SBR12        | SBR11    | SBR10    | SBR9      | SBR8      |

| 0x00 <b>41</b>                   | SCI2BDL           | SBR7        | SBR6       | SBR5        | SBR4         | SBR3     | SBR2     | SBR1      | SBR0      |

| 0x00 <b>42</b>                   | SCI2C1            | LOOPS       | SCISWAI    | RSRC        | М            | WAKE     | ILT      | PE        | PT        |

| 0x00 <b>43</b>                   | SCI2C2            | TIE         | TCIE       | RIE         | ILIE         | TE       | RE       | RWU       | SBK       |

| 0x00 <b>44</b>                   | SCI2S1            | TDRE        | TC         | RDRF        | IDLE         | OR       | NF       | FE        | PF        |

| 0x00 <b>45</b>                   | SCI2S2            | LBKDIF      | RXEDGIF    | 0           | RXINV        | RWUID    | BRK13    | LBKDE     | RAF       |

| 0x00 <b>46</b>                   | SCI2C3            | R8          | Т8         | TXDIR       | TXINV        | ORIE     | NEIE     | FEIE      | PEIE      |

| 0x00 <b>47</b>                   | SCI2D             | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

| 0x00 <b>48</b>                   | ICGC1             | HGO         | RANGE      | REFS        | CL           | KS       | OSCSTEN  | LOCD      | 0         |

| 0x00 <b>49</b>                   | ICGC2             | LOLRE       |            | MFD         | •            | LOCRE    |          | RFD       |           |

| 0x00 <b>4A</b>                   | ICGS1             | CL          | KST        | REFST       | LOLS         | LOCK     | LOCS     | ERCS      | ICGIF     |

| 0x00 <b>4B</b>                   | ICGS2             | 0           | 0          | 0           | 0            | 0        | 0        | 0         | DCOS      |

| 0x00 <b>4C</b>                   | ICGFLTU           | 0           | 0          | 0           | 0            |          | FI       | Т         |           |

| 0x00 <b>4D</b>                   | ICGFLTL           |             |            |             | FLT          | 7        |          |           |           |

| 0x00 <b>4E</b>                   | ICGTRM            |             |            |             | TRIN         | M        |          |           |           |

| 0x00 <b>4F</b>                   | 保留                | _           | _          | _           | _            | _        | _        | _         | _         |

| 0x00 <b>50</b>                   | SPI1C1            | SPIE        | SPE        | SPTIE       | MSTR         |          | CP       | OL        |           |

| 0x00 <b>51</b>                   | SPI1C2            | SPMIE       | 0          | 0           | MODFEN       | BIDIROE  | SPIMODE  | SPISWAI   | SPC0      |

| 0x00 <b>52</b>                   | SPI1BR            | 0           | SPPR2      | SPPR1       | SPPR0        | 0        | SPR2     | SPR1      | SPR0      |

| 0x00 <b>53</b>                   | SPI1S             | SPRF        | SPIMF      | SPTEF       | MODF         | 0        | 0        | 0         | 0         |

| 0x00 <b>54</b>                   | SPI1DH            | Bit 15      | 14         | 13          | 12           | 11       | 10       | 8         | Bit 8     |

| \$0055                           | SPI1DL            | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

| \$00 <b>56</b>                   | SPI1MH            | Bit 15      | 14         | 13          | 12           | 11       | 10       | 8         | Bit 8     |

| \$0057                           | SPI1ML            | Bit 7       | 6          | 5           | 4            | 3        | 2        | 1         | Bit 0     |

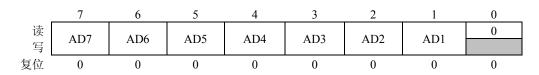

| \$0058                           | IIC1A             | AD7         | AD6        | AD5         | AD4          | AD3      | AD2      | AD1       | 0         |

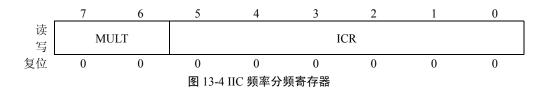

| 0x00 <b>59</b>                   | IIC1F             | MU          | JLT        |             |              | IC       | R        |           |           |

| 0x00 <b>5A</b>                   | пс1С              | IICEN       | IICIE      | MST         | TX           | TXAK     | RSTA     | 0         | 0         |

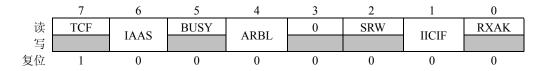

| 0x00 <b>5B</b>                   | IIC1S             | TCF         | IAAS       | BUSY        | ARBL         | 0        | SRW      | IICIF     | RXAK      |

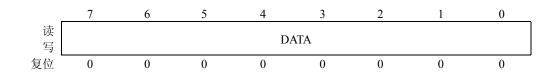

| 0x00 <b>5</b> C                  | IIC1D             |             |            | •           | DAT          | A        |          | •         |           |

| 0005D                            | IIC1C2            | GCAEN       | ADEXT      | 0           | 0            | 0        | AD10     | AD9       | AD8       |

| 0x005D                           |                   |             | i          |             |              | . ~      |          |           | .120      |

| 0x00 <b>5E</b>  | 保留       | _      | _     | _     | _     | _     | _     | _   | _     |

|-----------------|----------|--------|-------|-------|-------|-------|-------|-----|-------|

| 0x00 <b>5F</b>  | 保留       | _      | _     | _     | _     | _     | _     | _   | _     |

| 0x00 <b>60</b>  | TPM2SC   | TOF    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1 | PS0   |

| \$00 <b>61</b>  | TPM2CNTH | Bit 15 | 14    | 13    | 12    | 11    | 10    | 8   | Bit 8 |

| \$00 <b>62</b>  | TPM2CNTL | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| \$0063          | TPM2MODH | Bit 15 | 14    | 13    | 12    | 11    | 10    | 8   | Bit 8 |

| \$00 <b>64</b>  | TPM2MODL | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>65</b>  | TPM2C0SC | CH0F   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0   | 0     |

| \$00 <b>66</b>  | TPM2C0VH | Bit 15 | 14    | 13    | 12    | 11    | 10    | 8   | Bit 8 |

| \$00 <b>67</b>  | TPM2C0VL | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| 0x00 <b>68</b>  | TPM2C1SC | CH1F   | CH1IE | MS1B  | MS1A  | ELS1B | ELS1A | 0   | 0     |

| \$00 <b>69</b>  | TPM2C1VH | Bit 15 | 14    | 13    | 12    | 11    | 10    | 8   | Bit 8 |

| \$00 <b>6A</b>  | TPM2C1VL | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1   | Bit 0 |

| \$00 <b>6B</b>  | 保留       | _      | 1     |       | 1     |       | 1     |     |       |

| \$00 <b>6</b> C | 保留       | _      | -     | _     | -     | _     | -     | _   | _     |

| \$00 <b>6D</b>  | 保留       | _      | -     |       | -     | _     |       |     |       |

| \$00 <b>6E</b>  | 保留       | _      | _     |       |       |       |       |     |       |

| \$00 <b>6F</b>  | 保留       |        | _     | _     | _     | _     | _     | _   | _     |

表 4-3 中所示的高地址页寄存器比其他的 I/O 和控制寄存器要少访问,所以它们位于可直接寻址的存储器空间之外,开始于\$1800。

表 4-3 高地址页寄存器概要

|         |         |        | 衣 4-3  | ) 同地址贝1 | <b></b> |       |        |         |       |

|---------|---------|--------|--------|---------|---------|-------|--------|---------|-------|

| 地址      | 寄存器名称   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0 |

| \$1800  | SRS     | POR    | PIN    | COP     | ILCP    | 0     | ICG    | LVD     | 0     |

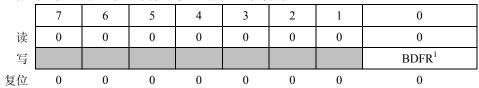

| \$1801  | SBDFR   | 0      | 0      | 0       | 0       | 0     | 0      | 0       | BDFR  |

| \$1802  | SOPT    | COPE   | COPT   | STOPE   | •       | 0     | 0      | •       | -     |

| \$1803  | SBDFR   | 0      | 0      | 0       | MPE     | 0     |        | MCSEL   |       |

| \$1804- | 保留      | -      | -      | -       | -       | -     | -      | -       | -     |

| \$1805  | 休田      | -      | -      | -       | -       | -     | -      | -       | -     |

| \$1806  | SDIDH   | REV3   | REV2   | REV1    | REV0    | ID11  | ID10   | ID9     | ID8   |

| \$1807  | SDIDL   | ID7    | ID6    | ID5     | ID4     | ID3   | ID2    | ID1     | ID0   |

| \$1808  | SRTISC  | RTIF   | RTIACK | RTICLKS | RTIE    | 0     | RTIS2  | RTIS1   | RTIS0 |

| \$1809  | SPMSC1  | LVDF   | LVDACK | LVDIE   | LVDRE   | LVDSE | LVDE   | $0^{1}$ | BGBE  |

| \$180A  | SPMSC2  | LVWF   | LVWACK | LVDV    | LVWV    | PPDF  | PPDACK | -       | PPDC  |

| \$180B  | 保留      | -      | -      | •       | -       | -     | -      | •       | -     |

| \$180C  | SOPT2   | -      | -      | -       | -       | -     | -      | -       | -     |

| \$180D- | /ti sin | -      | -      | -       | -       | -     | -      | -       | -     |

| \$180F  | 保留      | -      | -      | -       | -       | -     | -      | -       | -     |

| \$1810  | DBGCAH  | Bit 15 | 14     | 13      | 12      | 11    | 10     | 9       | Bit 8 |

| \$1811  | DBGCAL  | Bit 7  | 6      | 5       | 4       | 3     | 2      | 1       | Bit 0 |

| \$1812  | DBGCBH  | Bit 15 | 14     | 13      | 12      | 11    | 10     | 9       | Bit 8 |

| \$1813  | DBGCBL  | Bit 7  | 6      | 5       | 4       | 3     | 2      | 1       | Bit 0 |

| \$1814  | DBGFH   | Bit 15 | 14     | 13      | 12      | 11    | 10     | 9       | Bit 8 |

| \$1815  | DBGFL   | Bit 7  | 6      | 5       | 4       | 3     | 2      | 1       | Bit 0 |

| \$1816  | DBGC    | DBGEN  | ARM    | TAG     | BRKEN   | RWA   | RWAEN  | RWB     | RWBEN |

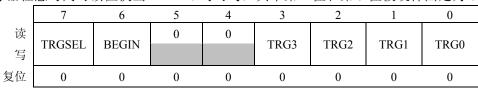

| \$1817  | DBGT    | TRGSEL | BEGIN  | 0       | 0       | TRG3  | TRG2   | TRG1    | TRG0  |

| \$1818  | DBGS    | AF     | BF     | ARMF    | 0       | CNT3  | CNT2   | CNT1    | CNT0  |

| \$1819- | /日 郊    | -      | -      | -       | -       | -     | -      | -       | -     |

| \$181F  | 保留      | -      | -      | -       | -       | -     | -      | -       | -     |

| \$1820  | FCDIV   | DIVLD  | PRDIV8 | DIV5    | DIV4    | DIV3  | DIV2   | DIV1    | DIV0  |

| \$1821  | FOPT    | KEYEN  | FNORED | 0       | 0       | 0     | 0      | SEC01   | SEC00 |

| \$1822  | 保留      | -      | -      | -       | -       | -     | -      | -       | -     |

| \$1823  | FCNFG   | 0      | 0      | KEYACC  | 0       | 0     | 0      | 0       | 0     |

| \$1824  | FPROT   | FPOPEN | FPDIS  | FPS2    | FPS1    | FPS0  | 0      | 0       | 0     |

|         |         |        |        |         |         |       |        |         |       |

| \$1825  | FSTAT                 | FCBEF        | FCCF   | FPVIOL    | FACCERR     | 0          | FBLANK | 0      | 0      |

|---------|-----------------------|--------------|--------|-----------|-------------|------------|--------|--------|--------|

| \$1826  | FCMD                  | FCMD7        | FCMD6  | FCMD5     | FCMD4       | FCMD3      | FCMD2  | FCMD1  | FCMD0  |

| \$1827- | 保留                    | -            | -      | -         | -           | -          | -      | -      | -      |

| \$182F  | 休田                    | -            | -      | -         | -           | -          | -      | -      | -      |

| 0x1830  | TPM3SC <sup>2</sup>   | TOF          | TOIE   | CPWMS     | CLKSB       | CLKSA      | PS2    | PS1    | PS0    |

| 0x1831  | TPM3CNTH <sup>2</sup> | Bit 15       | 14     | 13        | 12          | 11         | 10     | 9      | Bit 8  |

| 0x1832  | TPM3CNTL <sup>2</sup> | Bit 7        | 6      | 5         | 4           | 3          | 2      | 1      | Bit 0  |

| 0x1833  | TPM3MODH <sup>2</sup> | Bit 15       | 14     | 13        | 12          | 11         | 10     | 9      | Bit 8  |

| 0x1834  | TPM3MODL <sup>2</sup> | Bit 7        | 6      | 5         | 4           | 3          | 2      | 1      | Bit 0  |

| 0x1835  | TPM3C0SC <sup>2</sup> | CH0F         | CH0IE  | MS0B      | MS0A        | ELS0B      | ELS0A  | 0      | 0      |

| 0x1836  | TPM3C0VH <sup>2</sup> | Bit 15       | 14     | 13        | 12          | 11         | 10     | 9      | Bit 8  |

| 0x1837  | TPM3C0VL <sup>2</sup> | Bit 7        | 6      | 5         | 4           | 3          | 2      | 1      | Bit 0  |

| 0x1838  | TPM3C1SC <sup>2</sup> | CH1F         | CH1IE  | MS1B      | MS1A        | ELS1B      | ELS1A  | 0      | 0      |

| 0x1839  | TPM3C1VH <sup>2</sup> | Bit 15       | 14     | 13        | 12          | 11         | 10     | 9      | Bit 8  |

| 0x183A  | TPM3C1VL <sup>2</sup> | Bit 7        | 6      | 5         | 4           | 3          | 2      | 1      | Bit 0  |

| \$183B- | 保留                    | -            | -      | -         | -           | -          | -      | -      | -      |

| \$183F  |                       | -            | -      | -         | -           | -          | -      | -      | -      |

| 0x1840  | PTAPE                 | PTAPE7       | R      | R         | R           | R          | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841  | PTASE                 | PTASE7       | R      | R         | R           | R          | PTASE2 | PTASE1 | PTASE0 |

| 0x1842  | PTADS                 | PTADS7       | R      | R         | R           | R          | PTADS2 | PTADS1 | PTADS0 |

| 0x1843  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x1844  | PTBPE                 | R            | R      | R         | R           | PTBPE3     | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1845  | PTBSE                 | R            | R      | R         | R           | PTBSE3     | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x1846  | PTBDS                 | R            | R      | R         | R           | PTBDS3     | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x1847  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x1848  | PTCPE                 | 0            | R      | PTCPE5    | PTCPE4      | PTCPE3     | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1849  | PTCSE                 | 0            | R      | PTCSE5    | PTCSE4      | PTCSE3     | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x184A  | PTCDS                 | 0            | R      | PTCDS5    | PTCDS4      | PTCDS3     | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x184B  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x184C  | PTDPE                 | R            | R      | R         | R           | PTDPE3     | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x184D  | PTDSE                 | R            | R      | R         | R           | PTDSE3     | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x184E  | PTDDS                 | R            | R      | R         | R           | PTDDS3     | PTDDS2 | PTDDS1 | PTDDS0 |

| 0x184F  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x1850  | PTEPE                 | PTEPE7       | PTEPE6 | PTEPE5    | PTEPE4      | PTEPE3     | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x1851  | PTESE                 | PTESE7       | PTESE6 | PTESE5    | PTESE4      | PTESE3     | PTESE2 | PTESE1 | PTESE0 |

| 0x1852  | PTEDS                 | PTEDS7       | PTEDS6 | PTEDS5    | PTEDS4      | PTEDS3     | PTEDS2 | PTEDS1 | PTEDS0 |

| 0x1853  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x1854  | PTFPE                 | R            | PTFPE6 | PTFPE5    | PTFPE4      | R          | R      | PTFPE1 | PTFPE0 |

| 0x1855  | PTFSE                 | R            | PTFSE6 | PTFSE5    | PTFSE4      | R          | R      | PTFSE1 | PTFSE0 |

| 0x1856  | PTFDS                 | R            | PTFDS6 | PTFDS5    | PTFDS4      | R          | R      | PTFDS1 | PTFDS0 |

| 0x1857  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x1858  | PTGPE                 | 0            | PTGPE6 | PTGPE5    | PTGPE4      | PTGPE3     | PTGPE2 | PTGPE1 | PTGPE0 |

| 0x1859  | PTGSE                 | 0            | PTGSE6 | PTGSE5    | PTGSE4      | PTGSE3     | PTGSE2 | PTGSE1 | PTGSE0 |

| 0x185A  | PTGDS                 | 0            | PTGDS6 | PTGDS5    | PTGDS4      | PTGDS3     | PTGDS2 | PTGDS1 | PTGDS0 |

| 0x185B  | 保留                    | _            | _      | _         | _           | _          | _      | _      | _      |

| 0x185F  |                       | -            |        |           |             |            |        |        |        |

|         | 主 4 6 由配二的            | и. п. 🗀 и. ы |        | ~ ~ nn /> | <del></del> | A L. pp. 1 | - 1    | A      |        |

表 4-5 中所示的非易失性 FLASH 寄存器位于 FLASH 存储器中。包括两个 FLASH 存储器模块初始化寄存器和一个 8 字节的密钥,这个密钥用于获得对加密存储器的访问权。在复位后,FLASH 存储器的非易失性寄存器中 NVPROT 和 NVOPT 的内容被转移到相应的位于高页面寄存器中的 FPROT 和 FOPT 工作寄存器中,从而控制加密和阻止保护选项。

| 地址                | 寄存器名称     | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|-----------|-------|--------|-------|-------|-------|-------|-------|-------|

| \$FFB0-<br>\$FFB7 | NVBACKKEY | 8字节密钥 |        |       |       |       |       |       |       |

| \$FFB8-<br>\$FFBC | 保留        | -     | -      | -     | -     | -     | -     | -     | -     |

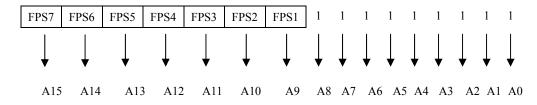

| \$FFBD            | NVPROT    | FPS7  | FPS6   | FPS5  | FPS4  | FPS3  | FPS2  | FPS1  | FPDIS |

| \$FFBE            | 保留(1)     | -     | -      | -     | -     | -     | -     | -     | -     |

| \$FFBF            | NVOPT     | KEYEN | FNORED | 0     | 0     | 0     | 0     | SEC01 | SEC00 |

表 4-4 非易失性寄存器概要

注: 1、这个位置可用于存储ICG的工厂预设值。

如果密钥使能位(KEYEN)为"1",8 字节的密钥将被用于暂时性的跳出存储器的安全保护模式。密钥机制只能通过在安全模式下运行的用户代码访问(密钥不可直接通过背景调试命令键入)。当 KEYEN 标志位为 0 时,密钥功能失效。如果密钥不可用,离开安全保护模式的唯一途径就是整体擦除 FLASH 存储器(通常通过背景调试接口),并且校验 FLASH存储器为空。为避免在下一次复位后又返回安全保护模式,向安全位(SEC01:SEC00)写入(1:0)进入非安全状态即可。

#### 4.3 RAM

MC9S08AC16 系列包含静态 RAM。可以使用更高效的直接地址寻址方式访问 RAM 中低于 0x0100 的地址。这一区域的每一位都可以用位操作指令(BCLR,BSET,BRCLR,BRSET)来访问。将访问最频繁的程序变量放在这个区域。

当 MCU 处于低压等待,STOP2,STOP3 模式时,RAM 保持数据。上电时,RAM 的内容被重新初始化。如果所提供的电压不小于RAM 所需的最小电压,RAM 数据不会被任何复位影响。

为了和以前的 M68HC05 MCU 兼容,HCS08 初始化时栈指针定为 0x00FF。在 MC9S08AC16 系列中,通常重新初始化栈指针指向 RAM 的顶端,这样直接页 RAM 可以用于频繁访问的 RAM 变量和可位寻址的程序变量。在重启初始化程序中包括接下来的两条指令(在 Freescale 提供的文件中 RamLast 等于 RAM 的最高地址)。

| LDHX | #RamLast+1 | ;指示上一个RAM    |

|------|------------|--------------|

| TXS  |            | ;SP<-(H:X-1) |

#### 44 FLASH

FLASH 主要用于程序存储。在线编程允许应用程序在最后一次编译以后下载到FLASH 存储器中。允许通过单一连线的背景调试接口对整个数组写入。因为对 FLASH 的擦除和写入操作不需要特殊的电压,在线应用程序编程(IAP)可以通过一些其他软件控制的通信方式进行下载。在线编程和 IAP 的详细信息请参见 "HCS08 Family Reference Manual, Volume I",它的飞思卡尔文档顺序号是 HCS08RMv1/D。

#### 4.4.1 特征

FLASH 有以下特征:

- FLASH 容量

- MC9S08AC16 和 MC9S08AW16: 16384 字节(每页 512 字节, 共 32 页)

- MC9S08AC8 和 MC9S08AW8: 8192 字节(每页 512 字节, 共 16 页)

- 一个电源提供写入和擦除。

- 用于快速写入和擦除操作的命令接口

- 在正常的电压和温度下,可高达 100000 次写入/擦除

- 灵活易用的块保护

- FLASH 和 RAM 的安全机制

- 自动低功耗低频率读访问

FLASH 存储模块包括完整的擦除/写入电压发生器和独立的指令处理状态机,可以实现自动字节写入,页擦除(512 字节的 FLASH)、整体擦除或空白检测命令的功能。这些命令是写在命令接口中的,状态标志可以报告错误并且可以指示命令是什么时候完成的。

在 FLASH 存储区的末端的 512、1K、2K、4K、8K、16K 或者 32K 字节的块可以进行 块保护。另外的控制位允许对整个 FLASH 区的 60K 字节进行块保护(见 4.7.4 节 FLASH 保护寄存器(FPROT 和 NVFPROT))。可以通过设置非易失性的初始化寄存器(NVFPROT)来设置块保护。可以使用安全机制来预防对 FLASH 和 RAM 存储内容的非法访问。用户可以使用密钥来取得安全模式下的存储器内容的访问控制。

#### 4.4.2 写入和擦除时间

在执行任何一条擦除或者写入命令之前,必须首先设置 FLASH 时钟分频寄存器 (FCDIV),将 FLASH 模块的内部时钟设到 150kHz 到 200kHz 之间(f<sub>FCLK</sub>), (见 4.6.1 节 FLASH 时钟分频寄存器 FCDIV),这个寄存器只能被写一次,所以一般在复位初始化中设置该寄存器。如果访问错误标志位(FSTAT 的 FACCERR)被置位 FCDIV 不能被写。用户在写 FCDIV 寄存器前确保 FACCERR 没有置位。设置好的时钟周期(1/ f<sub>FCLK</sub>)被命令处理器用来对擦除和写入脉冲进行计时。这些计时脉冲的整数倍作为时钟被命令处理器用来完成一个擦除或者写入的命令。

表 4-5 描述了写入和擦除的时间。总线时钟频率和 FCDIV 决定了 FLCK 的频率( $f_{FCLK}$ ) FCLK 一个周期的时间是  $t_{FCLK}$ =1/ $f_{FCLK}$ 。写入和擦除时间由许多 FCLK 时钟周期组成,绝对时间是  $t_{FCLK}$ =5 $\mu$ s。这个时间也包括了命令状态机和允许与禁止写入和擦除电压使用的时间。

| 参数       | FCLK周期 | 时间(FCLK=200KHz)   |

|----------|--------|-------------------|

| 字节写入     | 9      | 45μs              |

| 字节写入(突发) | 4      | 20μs <sup>1</sup> |

| 页擦除      | 4000   | 20ms              |

| 整体擦除     | 20000  | 100ms             |

表 4-5 写入和擦除时间

(1)不包括开始/结束的时间花费

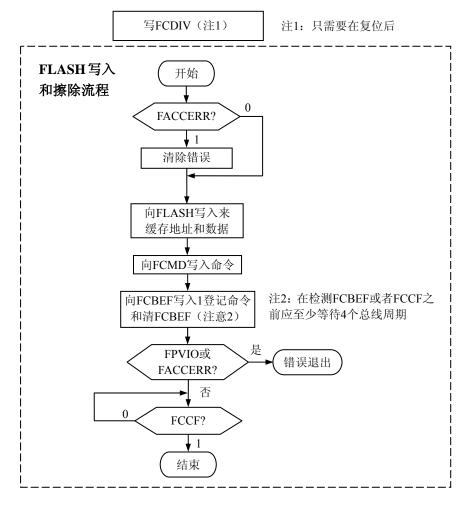

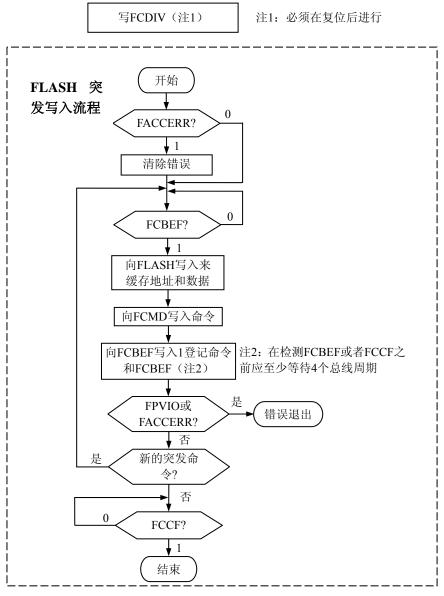

### 4.4.3 写入和擦除命令的执行

执行任何命令的步骤如下所列。FCDIV 寄存器必须被初始化,并且在开始执行命令前要将所有的错误标志清零。命令的执行步骤是:

● 向要擦除的 FLASH 区域的一个地址写入一个数值。这个写入的地址和数值的信息将被放在命令缓冲区中。命令序列的第一步就是进行这个写入。对擦除和空白检测命令来说,这个数据的值是不重要的。但是对于页擦除命令,这个地址必须是要擦除的 512 字节的 FLASH 页中的任意一个地址。对于整体擦除命令和空白检测命令,这个地址可以是 FLASH 存储器中的任意一个地址。512 字节的一整页

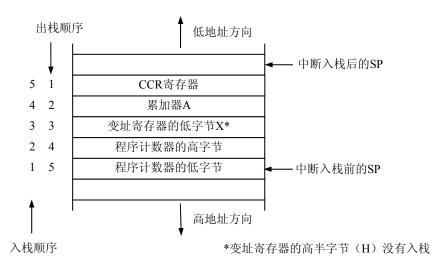

是 FLASH 中可以擦除的最小块。在 60K 版本中,用户可存取的块小于 512 字节的情况有两种,分别是 RAM 后面的第一页和高地址寄存器。

注:

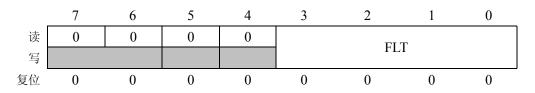

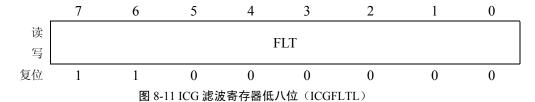

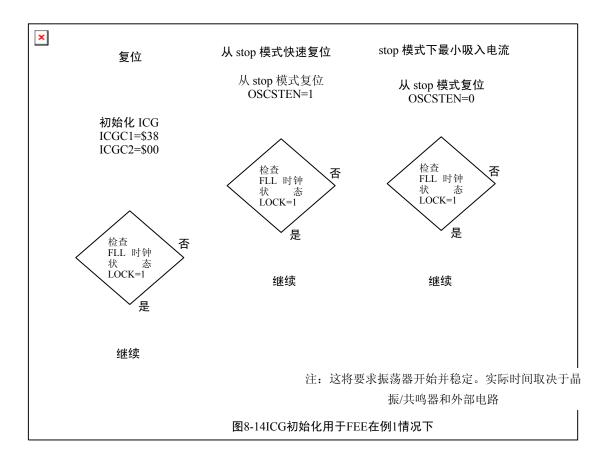

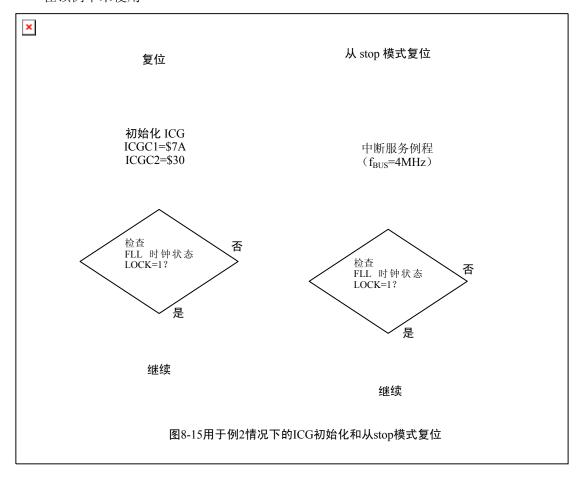

完成一次写入操作后,FLASH 内的每个字节只能被写入一次。如果一个位已经被写入,再次向这个字节写入一些位需要先擦除这个字节或整体擦除 FLASH。未经擦除而直接写入会影响存储在 FLASH 内的数据。