# MC9S08JS16

参考手册

苏州大学飞思卡尔嵌入式系统研发中心翻译

http://sumcu.suda.edu.cn

2009年11月

# MC9S08JS16 系列特点

#### 8 位 HCS08 中央处理单元 (CPU)

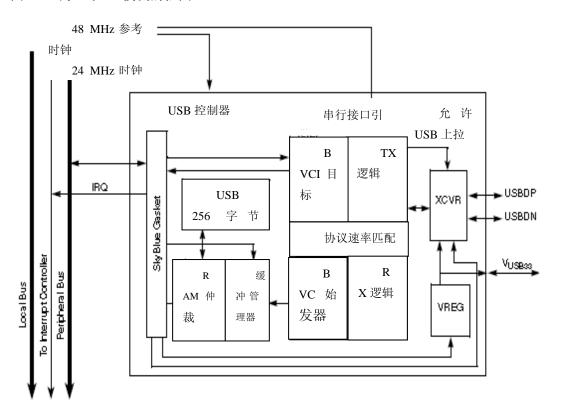

- 48-MHz HCS08CPU(中央处理单元)

- 24-MHz 内部总线频率

- HC08 指令集,增加了 BGND 指令

- 支持高达 32 个中断/复位源

#### 存储器选项

- 高达 16KB 的片上在线可编程 FLASH 存储器,有块保护和安全选项

- 高达 512B 的片上 RAM

- 256B 的 USB RAM

#### 时钟源选项

- 时钟源选项包括晶体,蜂鸣器,外部时钟,或能够 NVM 调整的精确的内部集成时 钟

- MCG(通用时钟产生器)-PLL, FLL; 带修正的内部参考时钟。

#### 系统保护

- 可选的系统正常操作(COP)复位,使用独立的1KHz的内部时钟源或总线时钟运行

- 低压检测复位或中断

- 非法操作符检测复位

- 非法地址检测复位

#### 省电模式

● 增加了两种停止模式

#### 加载 USB

- MASS 位整体擦除闪存阵列

- 部分擦除闪存阵列-擦除除起始的 1KB 外的所有块。

- 编程区

#### 外部设备

- USB-USB 2.0 全速(12Mbps),含专用片上 3.3V 调节器和收发器;支持端口 0 以及多达 6 个附加端点。

- SPI-8 或 16 位可选的串行外设接口模块并有硬件匹配功能模块

- SCI-一个串行通信接口模块,可选的 13 位停止符;全双工反向不归零;LIN 扩展主机停止位产生; LIN 从机扩展停止位检测;活动边沿唤醒

- MTIM-8 位模数计数器,含 8 位预分频因子和溢出中断

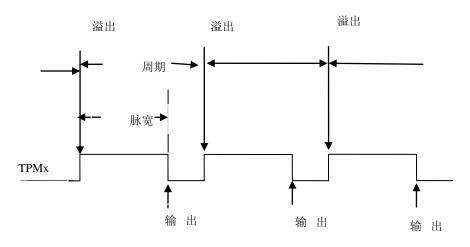

- 定时器-一个 2 通道 16 位定时器/脉宽调制(TPM)模块;每个定时器在每个通道上都有可选的输入捕捉,输出比较,PWM。每个定时器在每个通道上都可以配置

为带缓冲,中心PWM(CPWM)

- KBI-8 引脚键盘中断模块

- RTC-含有二进制或十进制与分频器的实时计数器

- CRC-带 16 位移位寄存器的硬件 CRC 产生器电路;基于多项式 x^16+x^12+x^5+1 的 CRC16-CCITT 校验

# 输入/输出

- 输入时,每个端口都有软件选择的上拉电阻

- 输出时,每个端口都有软件选择的转换速率控制

- 输出时,每个端口都有软件选择的驱动强度

- 主机复位引脚和上电复位(POR)

- RESET, IRQ, BKGD/MS 引脚在内部上拉以减小系统消耗

### 封装选择

- 24 引脚 QFN

- 20 引脚 SOIC

# 版本历史

为了提供最先进的最新资料,我们在万维网上发布的资料是最新修改的。您的印刷本可能是此修订前的版本。若需核查您是否具有最新的可用信息,请参考: <a href="http://freescale.com">http://freescale.com</a> 下面描述了此版本与历史版本的所发生的变化

| 版本号 | 版本日期       | 变化描述                    |

|-----|------------|-------------------------|

| 1   | 8/27/2008  | 最初发行版                   |

|     |            | 0xFFAE 和 0xFFAF 的寄存器内容发 |

|     |            | 生改变, 见表 4-4 以及出厂修正值     |

| 2   | 12/17/2008 | 的描述                     |

|     |            | KBI特性部分的删除重复信息          |

|     |            | 在复位为 0 后,改变 PTASE/PTBSE |

|     |            | 寄存器的默认值                 |

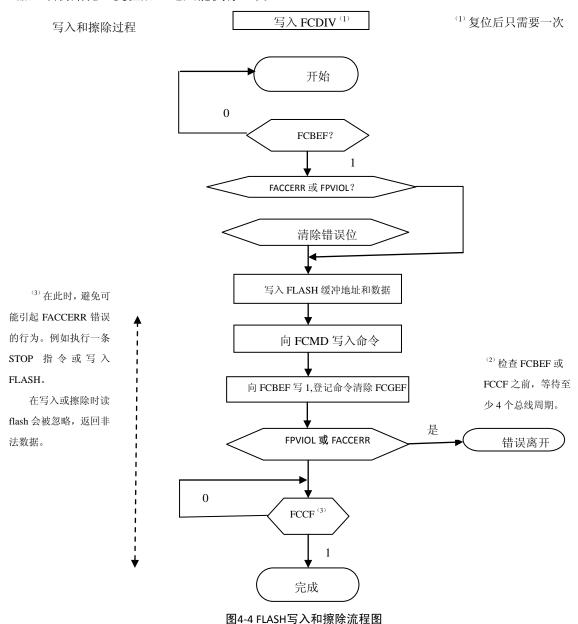

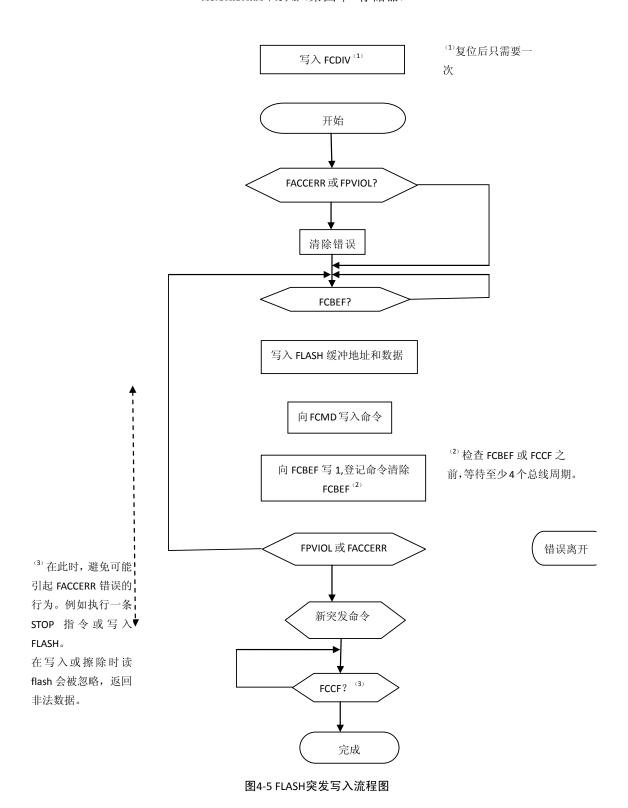

| 3   | 3/6/2009   | 更新图 4-4 和图 4-5          |

| 4   | 4/24/2009  | 增加了 MC9S08JS16L 和       |

|     |            | MC9S08JS8L 信息           |

# 目 录

| 第一章 导言                             | 9  |

|------------------------------------|----|

| 1.1 芯片概述                           | 9  |

| 1.2 MCU 框图                         |    |

| 1.3 系统时钟分布                         | 11 |

| 第二章 引脚和连接                          | 13 |

| 2.1 简介                             | 12 |

| 2.2 芯片引脚布局                         |    |

| 2.3 推荐系统连接                         |    |

| 2.3.1 电源(VDD, VSS, VSSOSC, VUSB33) |    |

| 2.3.2 振荡器(XTAL ,EXTAL )            |    |

| 2.3.3 RESET 引脚                     | 15 |

| 2.3.4 背景/模式选择(BKGD/MS)             |    |

| 2.3.5 引导程序模式选择(BLMS)               |    |

| 2.3.6 USB 数据引脚(USBDP,USBDN)        |    |

| 2.3.7 GPIO 及外设端口                   |    |

| 第三章 操作模式                           |    |

| 3.1 简介                             | 18 |

| 3.2 特性                             |    |

| 3.3 运行模式                           |    |

| 3.4 激活背景模式                         |    |

| 3.5 等待模式                           |    |

| 3.6 停止模式                           |    |

| 3.6.1 STOP3 模式                     |    |

| 3.6.2 STOP2 模式                     |    |

| 3.6.3 停止模式下片内外设模块                  | 21 |

| 第四章 存储器                            | 23 |

| 4.1 简介 MC9S08JS16 系列存储器映像          | 23 |

| 4.1.1 复位和中断向量分配                    | 23 |

| 4.2 寄存器地址和位分配                      | 24 |

| 4.3 RAM(系统 RAM)                    | 30 |

| 4.4 USB RAM                        | 30 |

| 4.5 引导程序 ROM                       | 30 |

| 4.5.1 外部信号描述                       | 31 |

| 4.5.2 操作模式                         | 31 |

| 4.5.3 FLASH 存储映像                   | 32 |

|     | 4.5.4 引导程序操作                      | 33 |

|-----|-----------------------------------|----|

| 4.6 | FLASH                             | 34 |

|     | 4.6.1 特点                          | 34 |

|     | 4.6.2 写入和擦除时间                     | 35 |

|     | 4.6.3 编程和擦除命令的执行                  | 35 |

|     | 4.6.4 批量写入                        | 36 |

|     | 4.6.5 访问错误                        | 38 |

|     | 4.6.6 FLASH 块保护                   | 39 |

|     | 4.6.7 向量重定向                       | 39 |

| 4.7 | 安全性                               | 40 |

| 4.8 | FLASH 寄存器和控制位                     | 41 |

|     | 4.8.1 FLASH 时钟分频寄存器(FCDIV)        | 41 |

|     | 4.8.2 FLASH 选项寄存器(FOPT 和 NVOPT)   | 42 |

|     | 4.8.3 FLASH 配置寄存器(FCNFG)          | 43 |

|     | 4.8.4 FLASH 保护寄存器(FPROT 和 NVPROT) | 43 |

|     | 4.8.5 FLASH 状态寄存器(FSTAT)          | 43 |

|     | §4.8.6 FLASH 命令寄存器(FCMD)          | 44 |

| 第五章 | 复位、中断和系统控制                        | 46 |

| 5.1 | 引言                                | 46 |

| 5.2 | 特点                                | 46 |

| 5.3 | MCU 复位                            | 46 |

| 5.4 | 计算机正常运行(COP)看门狗                   | 46 |

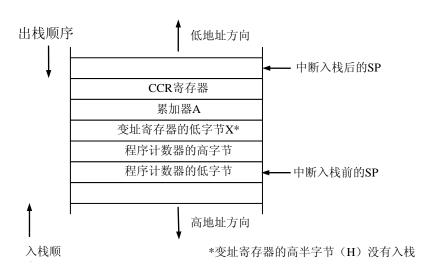

| 5.5 | 中断                                | 47 |

|     | 5.5.1 中断堆栈的帧                      |    |

|     | 5.5.2 外部中断请求(IRQ)引脚               | 48 |

|     | 5.5.3 中断向量,源和本地屏蔽                 | 49 |

| 5.6 | 低电压检测(LVD)系统                      | 50 |

|     | 5.6.1 上电复位操作                      | 50 |

|     | 5.6.2 LVD 复位操作                    |    |

|     | 5.6.3 低电压警告(LVW)                  |    |

| 5.7 | 复位,中断,系统控制寄存器以及控制位                | 51 |

|     | 5.7.1 中断引脚请求状态和控制寄存器(IRQSC)       | 51 |

|     | 5.7.2 系统复位状态寄存器(SRS)              |    |

|     | 5.7.3 系统背景调试强制复位寄存器 (SBDFR)       |    |

|     | 5.7.4 系统选项寄存器 1 (SOPT1)           |    |

|     | 5.7.5 系统选项寄存器 2 (SOPT2)           |    |

|     | 5.7.6 FLASH 保护失败寄存器(FPROTD)       |    |

|     | 5.7.7 SIGNATURE 寄存器(SIGNATURE)    |    |

|     | 5.7.8 系统设备识别寄存器(SDIDH,SDIDL)      |    |

|     | 5.7.9 系统能源管理状态和控制 1 寄存器(SPMSC1)   |    |

|     | 5.7.8 系统能源管理状态和控制 2 寄存器(SPMSC2)   | 56 |

| 第六章 | 并行输入/输出控制                         | 58 |

| 6.1 | <b>企</b> 组                        | 58 |

| 6.3 | 3 端口控制                                | 58 |

|-----|---------------------------------------|----|

|     | 6.3.1 内部上拉允许                          | 58 |

|     | 6.3.2 输出速率转换控制允许                      | 58 |

|     | 6.3.3 输出驱动强度选择                        | 59 |

| 6.4 | 4 在停止模式下引脚的行为                         | 59 |

| 6.5 | 5 并行 I/O 和引脚控制寄存器                     | 59 |

|     | 6.5.1 端口 A I/O 寄存器(PTAD 和 PTADD)      | 59 |

|     | 6.5.2 端口A 引脚控制寄存器 (PTAPE,PTASE,PTADS) | 60 |

|     | 6.5.3 端口 B I/O 寄存器(PTBD 和 PTBDD)      | 61 |

|     | 6.5.4 端口B 引脚控制寄存器(PTBPE,PTBSE,PTBDS)  | 61 |

| 第七章 | 中央处理单元(S08CPUV2)                      | 63 |

| 7.  | 1 介绍                                  | 63 |

|     | 7.1.1 特征                              |    |

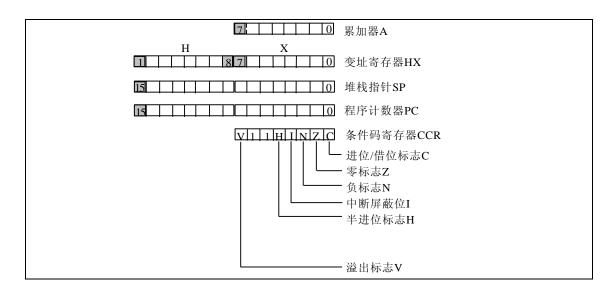

| 7.2 | 2 编程结构和 CPU 寄存器                       | 63 |

|     | 7.2.1 累加器(A)                          |    |

|     | 7.2.2 索引寄存器(H:X)                      |    |

|     | 7.2.3 堆栈指针(SP)                        |    |

|     | 7.2.4 程序计数器(PC)                       |    |

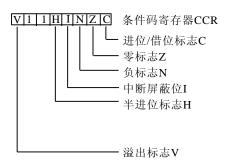

|     | 7.2.5 条件码寄存器(CCR)                     |    |

| 7.3 | 3 寻址模式                                |    |

|     | 7.3.1 内在寻址方式(INH)                     | 66 |

|     | 7.3.2 相对寻址方式(REL)                     | 66 |

|     | 7.3.3 立即寻址方式(IMM)                     | 66 |

|     | 7.3.4 直接寻址方式(DIR)                     | 66 |

|     | 7.3.5 扩展寻址方式(EXT)                     | 66 |

|     | 7.3.6 变址寻址方式                          | 66 |

| 7.4 | 4 特殊操作                                | 67 |

|     | 7.4.1 复位序列                            | 67 |

|     | 7.4.2 中断序列                            | 67 |

|     | 7.4.3 等待模式                            | 68 |

|     | 7.4.4 停止模式                            | 68 |

|     | 7.4.5 背景模式                            | 68 |

| 7.5 | 5 HCS08 指令设置摘要                        | 68 |

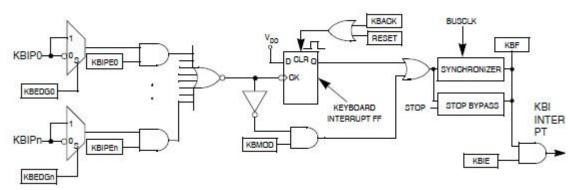

| 第八章 | 注键盘中断(S08KBIV2)                       | 84 |

| 8.  | 1 简介                                  | 84 |

|     | 8.1.1 特征                              | 86 |

|     | 8.1.2 操作模式                            |    |

|     | 8.1.3 框图                              |    |

| 8.2 | 2 外部信号描述                              |    |

|     | 3 寄存器定义                               |    |

|     | 8.3.1 KBI 状态和控制寄存器(KBISC)             | 87 |

|     | 8.3.2 KBI 引脚使能寄存器(KBIPE)              |    |

|     | 8.3.3 KBI 沿探测寄存器(KBIES)               | 88 |

|        | 8.4.1 沿敏感                    | 88  |

|--------|------------------------------|-----|

|        | 8.4.2 边沿电平敏感                 | 88  |

|        | 8.4.3 KBI 上拉/下拉电阻            | 88  |

|        | 8.4.4 KBI 初始化                | 89  |

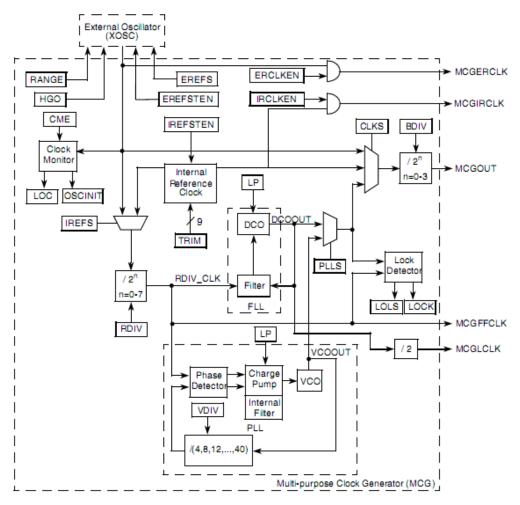

| 第9章    | 多功能时钟发生器(S08MCGV1)           | 90  |

| 9.1    | 简介                           | 90  |

|        | 9.1.1 特点                     | 92  |

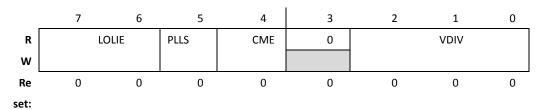

|        | 9.1.2 运行模式                   | 93  |

| 9.2    | 外部信号描述                       | 93  |

| 9.3    | 寄存器定义                        | 94  |

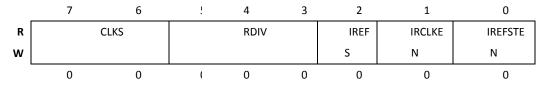

|        | 9.3.1 MCG 控制寄存器 1(MCGC1)     | 94  |

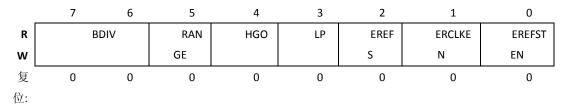

|        | 9.3.2 MCG 控制寄存器 2(MCGC2)     | 95  |

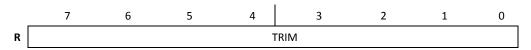

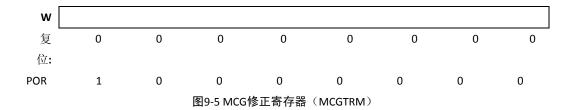

|        | 9.3.3 MCG 修正寄存器              | 95  |

|        | 9.3.4 MCG 状态和控制寄存器(MCGSC)    | 96  |

|        | 9.3.5 MCG 控制寄存器 3(MCGC3)     | 97  |

| 9.4    | 功能描述                         | 98  |

|        | 9.4.1 操作模式                   | 98  |

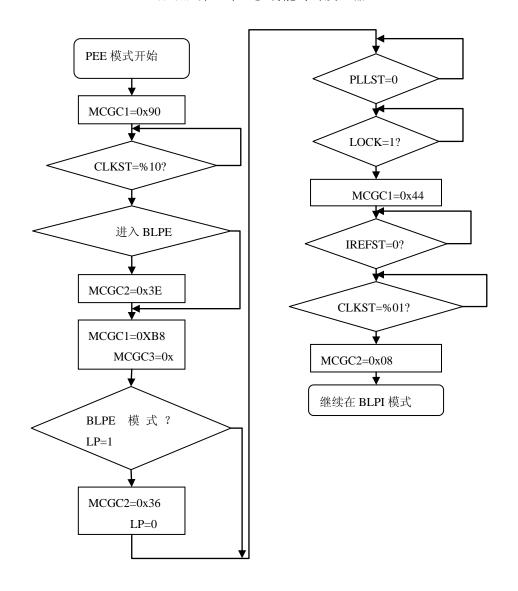

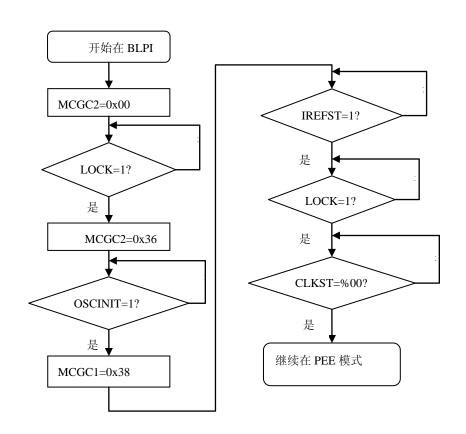

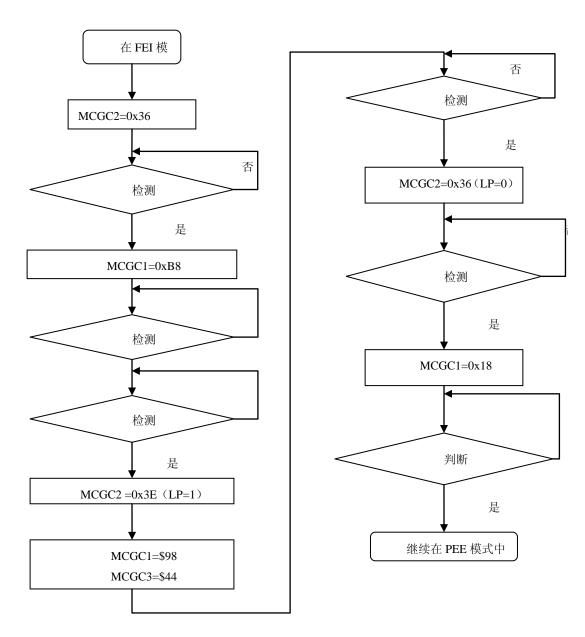

|        | 9.4.2 模式转换                   | 101 |

|        | 9.4.3 总线频率分频器                | 101 |

|        | 9.4.4 低功耗位的使用                | 101 |

|        | 9.4.5 内部参考时钟                 | 101 |

|        | 9.4.6 外部参考时钟                 | 102 |

|        | 9.4.7 混合频率时钟                 | 102 |

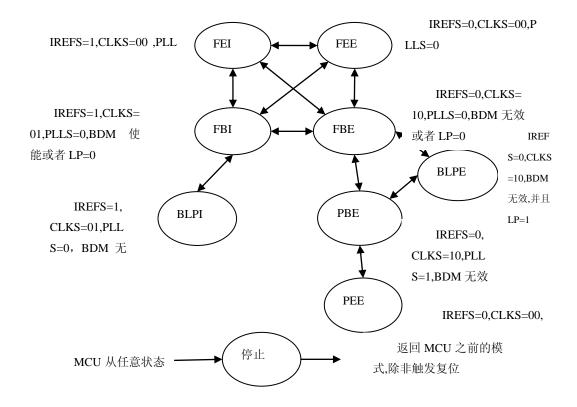

| 9.5    | 初始化/应用信息                     | 102 |

|        | 9.5.1 MCG 模块初始化序列            | 102 |

|        | 9.5.2 MGC 模式转换               | 103 |

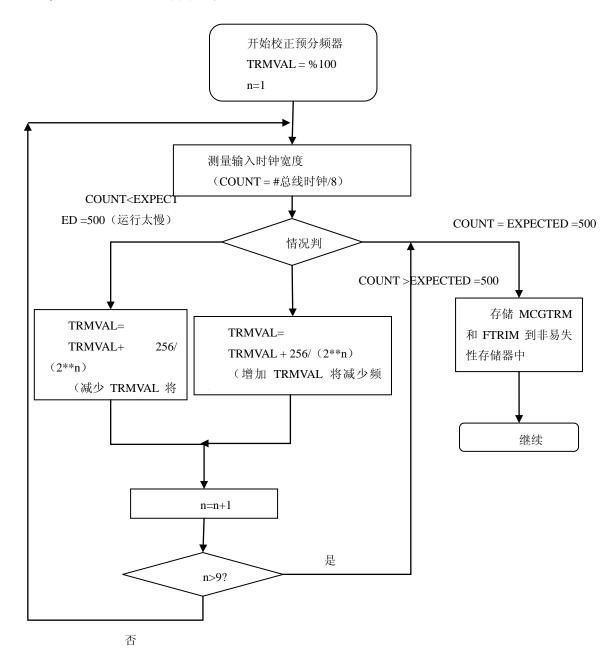

|        | 9.5.3 测定内部参考时钟(IRC)          | 111 |

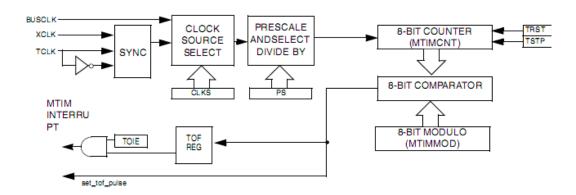

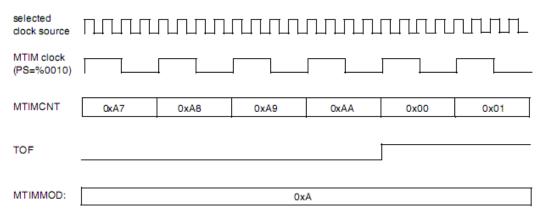

| 第十章    | 模数定时器(S08MTIMV1)             | 113 |

| 10.1   | 1 简介                         | 113 |

|        | 10.1.1 MTIM 配置信息             | 113 |

|        | 10.1.2 特性                    | 115 |

|        | 10.1.3 操作模式                  | 115 |

|        | 10.1.4 框图                    | 115 |

| 10.2   | 2 外部信号描述                     | 116 |

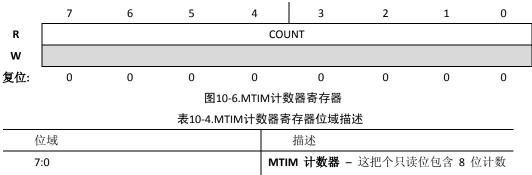

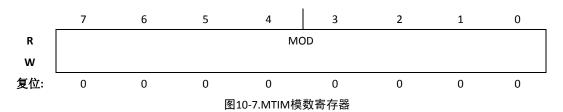

| 10.3   | 3 寄存器定义                      | 116 |

|        | 10.3.1 MTIM 状态和控制寄存器(MITMSC) | 117 |

|        | 10.3.2 MTIM 时钟配置寄存器(MTIMCLK) | 117 |

|        | 10.3.3 MTIM 计数器寄存器(MTIMCNT)  | 118 |

|        | 10.3.4 TIM 模数寄存器(MTIMMOD)    | 118 |

| 10.4   | 4 功能描述                       | 119 |

|        | 10.4.1 MTIM 运行实例             |     |

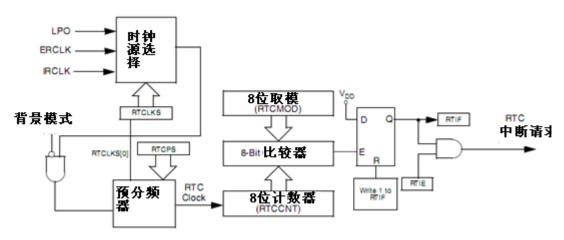

| 第 11 章 | 实时计数器 (S08RTCV1)             | 121 |

| 11.    | 1 介绍                              | 121 |

|--------|-----------------------------------|-----|

|        | 11.1.1 特性                         | 123 |

|        | 11.1.2 运行模式                       | 123 |

|        | 11.1.3 框图                         | 123 |

| 11.    | 2 外部信号描述                          | 124 |

| 11.    | 3 寄存器定义                           |     |

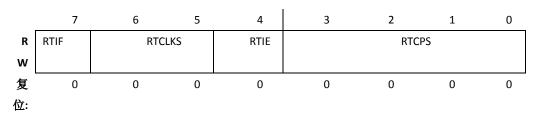

|        | 11.3.1 RTC 状态和控制寄存器(RTCSC)        | 124 |

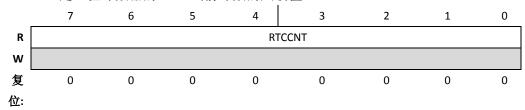

|        | 11.3.2 RTC 计数器寄存器(RTCCNT)         |     |

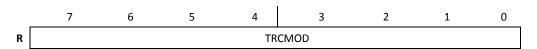

|        | 11.3.3 RTC 模块寄存器(RTCMOD)          |     |

| 11.    | 4 功能描述                            |     |

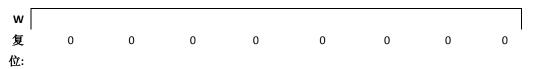

|        | 11.4.1 RTC 运行模式                   |     |

| 11.    | 5 初始化/应用信息                        | 127 |

| 第 12 章 | 章 串行通信接口(S08SCIV4)                | 129 |

| 12.    | 1 简介                              | 129 |

|        | 12.1.1 特性                         |     |

|        | 12.1.2 操作模式                       | 131 |

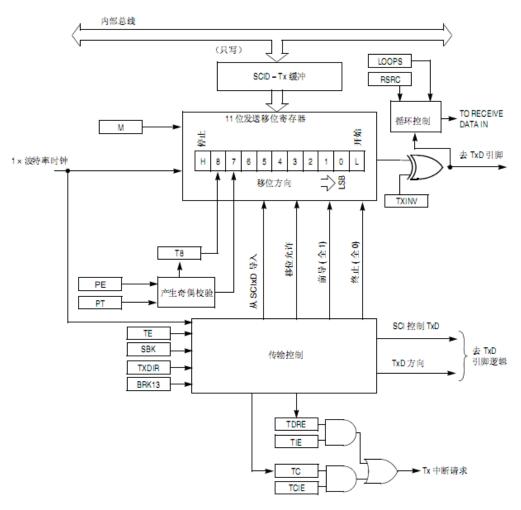

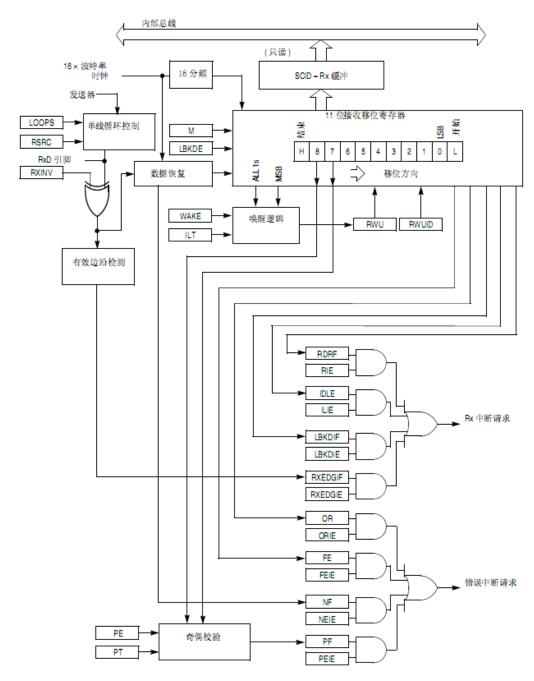

|        | 12.1.3 框图                         | 131 |

| 12.    | 2 寄存器定义                           | 133 |

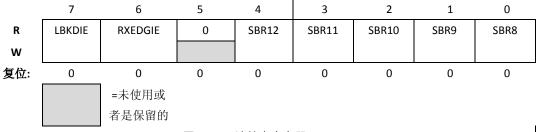

|        | 12.2.1 SCI 波特率寄存器 (SCIBDH,SCIBDL) | 133 |

|        | 12.2.2 SCI 控制寄存器 1(SCIC1)         | 134 |

|        | 12.2.3 SCI 控制寄存器 2(SCIC2)         | 135 |

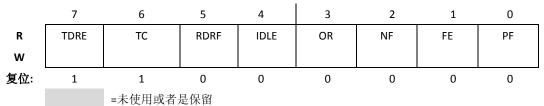

|        | 12.2.4 SCI 状态寄存器(SCIS1)           | 137 |

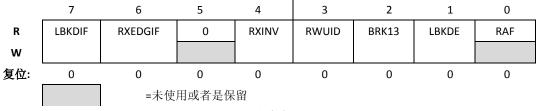

|        | 12.2.5 SCI 状态寄存器 2(SCIS2)         | 138 |

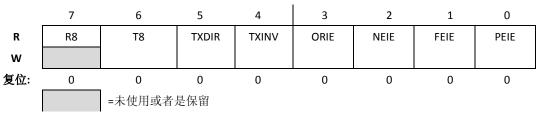

|        | 12.2.6 SCI 控制寄存器 3(SCIC3)         | 139 |

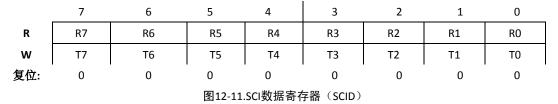

|        | 12.2.7 SCI 数据寄存器(SCID)            | 140 |

| 12.    | 3 功能描述                            | 140 |

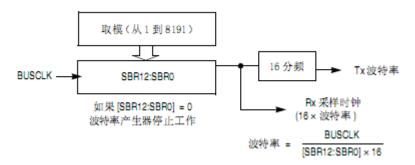

|        | 12.3.1 波特率发生                      | 140 |

|        | 12.3.2 发送功能描述                     | 141 |

|        | 12.3.3 接收功能描述                     | 142 |

|        | 12.3.4 中断和状态标志                    | 143 |

|        | 12.3.5 其他 SCI 功能                  | 144 |

| 第 13 章 | f 16 位串行外设接口(S08SPI16V1)          | 146 |

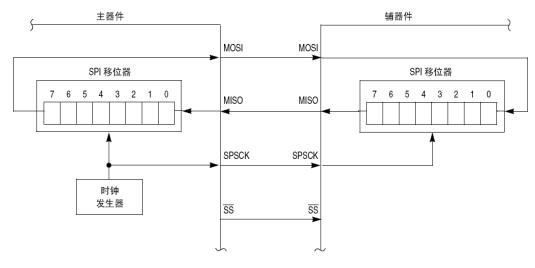

| 13.    | 1 简介                              | 146 |

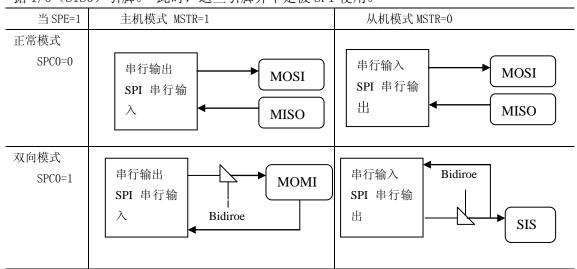

|        | 13.1.1 SPI 端口配置信息                 | 146 |

|        | 13.1.2 特性                         | 148 |

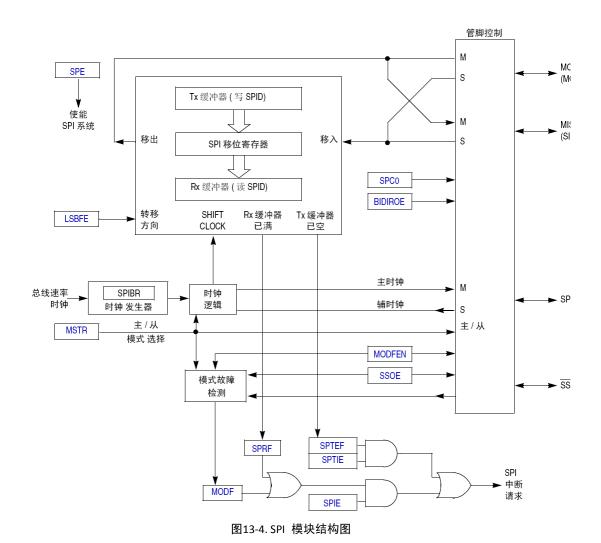

|        | 13.1.2 结构图                        | 149 |

|        | 13.1.3 SPI 结构图                    | 149 |

| 13.    | 2 外部信号描述                          | 151 |

|        | 13.2.1 SPSCK — SPI 串行时钟           | 151 |

|        | 13.2.2 MOSI —主数据输出, 从数据输入         | 151 |

|        | 13.2.3 MISO —主数据输入, 从数据输出         | 152 |

|        | 13.2.4 SS—从模式选择                   | 152 |

| 13.    | 3 寄存器定义                           | 152 |

| 13.3.1 SPI 控制寄存器 1(SPI1C1)            | 152  |

|---------------------------------------|------|

| 13.3.2 SPI 控制寄存器 2(SPI1C2)            | 153  |

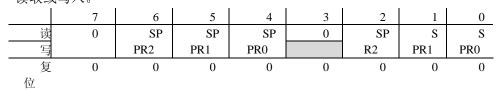

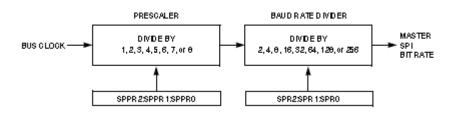

| 13.3.3 SPI 波特率寄存器(SPI1BR)             | 154  |

| 13.3.4 SPI 状态寄存器(SPI1S)               | 155  |

| 13.3.5 SPI 数据寄存器(SPIDH: SPIDL)        | 156  |

| 13.3.5 SPI 匹配寄存期(SPIMH: SPIML)        | 157  |

| 13.4 功能描述                             | 157  |

| 13.4.2 主机模式                           | 157  |

| 13.4.3 从机模式                           | 158  |

| 13.4.4 数据传输长度                         | 159  |

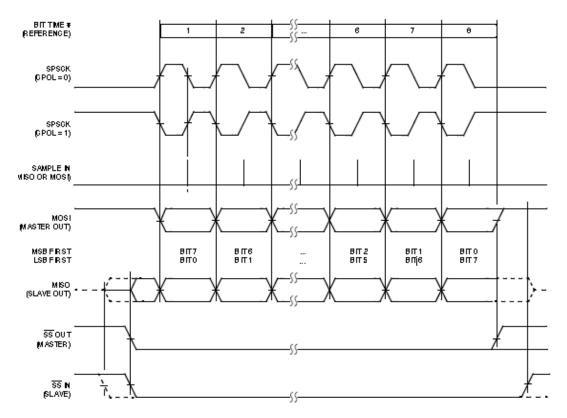

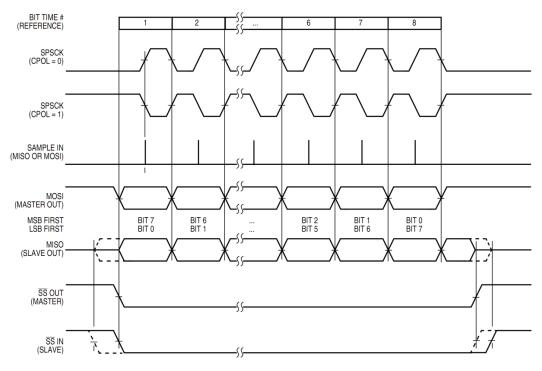

| 13.4.5 SPI 时钟格式                       | 159  |

| 13.4.6 SPI 波特率的产生                     | 161  |

| 13.4.7 特性                             | 162  |

| 13.4.8 错误发生条件                         |      |

| 13.8.1 模式故障错误                         |      |

| 13.4.9 低功耗模式                          |      |

| 13.4.10 SPI 中断                        | 164  |

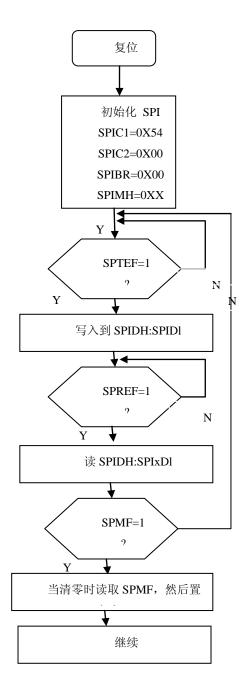

| 13.5 初始化/应用信息                         |      |

| 13.5.1 SPI 模块初始化例子                    | 165  |

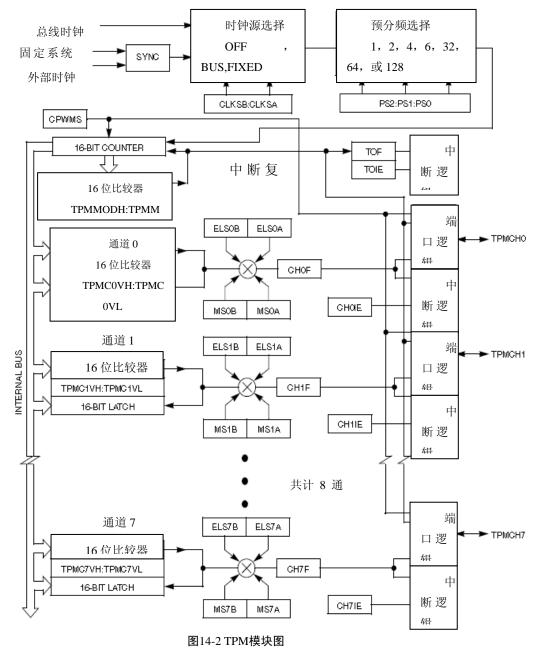

| 第十四章 定时器/脉冲调制器(S08TPMV3)              | 168  |

| 14.1 介绍                               | 168  |

| 14.2 特性                               | 168  |

| 14.3 TPMV3 与以前版本的不同之处                 | 170  |

| 14.3.1 从 TPMV1 迁移                     | 171  |

| 14.3.2 特性                             | 172  |

| 14.3.3 操作模式                           | 172  |

| 14.3.4 模块图                            | 173  |

| 14.4 信号描述                             | 174  |

| 14.4.1 详细信号描述                         | 175  |

| 14.5 寄存器定义                            | 177  |

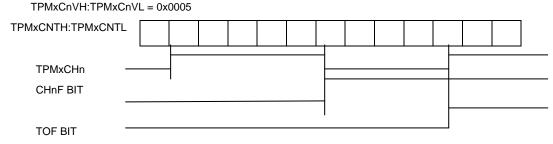

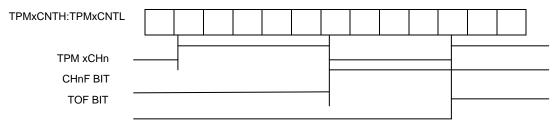

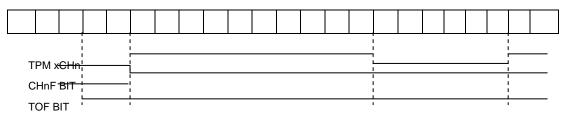

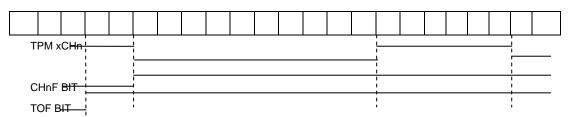

| 14.5.1 TPM 状态和控制寄存器(TPMxSC)           | 177  |

| 14.5.2 TPMM 计数寄存器(TPMxCNTH: TPMxCNTL) | 179  |

| 14.5.3 TPM 计数器模数寄存器(TPMxMODH:TPMxMODL | )179 |

| 14.5.4 TPM 通道 n 状态和控制寄存器(TPMxCnSC)    | 180  |

| 14.5.5 TPM 通道值寄存器(TPMxCnVH:TPMxCnVL)  | 181  |

| 14.6 功能描述                             |      |

| 14.6.1 计数器                            | 182  |

| 14.6.2 通道模式选择                         |      |

| 14.7 复位总览                             | 186  |

| 14.7.1 综述                             |      |

| 14.7.2 复位操作描述                         |      |

| 14.8 中断                               |      |

| 14.8.1 综述                             |      |

| 14.8.2 中断操作描述                         | 187  |

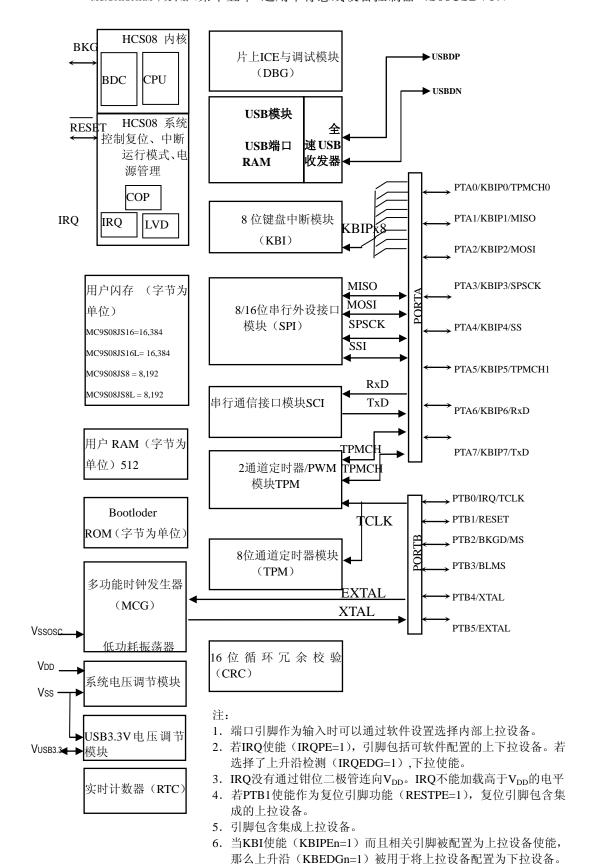

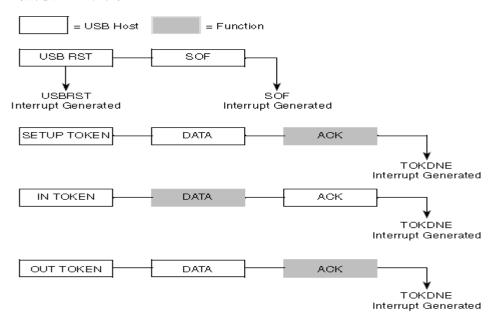

| 第十五章 通用串行总线设备控制器(S08USBV1)     | 190 |

|--------------------------------|-----|

| 15.1 引言                        | 190 |

| 15.1.1 时钟要求                    | 190 |

| 15.1.2 USB 悬挂模式的电流消耗           | 190 |

| 15.1.3 3.3V 稳压器                | 190 |

| 15.1.4 特性                      | 192 |

| 15.1.5 操作模式                    | 192 |

| 15.1.6 框图                      | 193 |

| 15.2 外部信号描述                    | 193 |

| 15.2.1 USBDP                   | 193 |

| 15.2.2 USBDN                   | 194 |

| 15.2.3 Vusb33                  |     |

| 15.3 寄存器定义                     |     |

| 15.3.1 USB 控制寄存器 0(USBCTL0)    |     |

| 15.3.2 外设 ID 寄存器(PERID)        |     |

| 15.3.3 外设 ID 反码寄存器(IDCOMP)     |     |

| 15.3.4 外设版本寄存器(REV)            |     |

| 15.3.5 中断状态寄存器(INTSTAT)        |     |

| 15.3.6 中断使能寄存器(INTENB)         | 197 |

| 15.3.7 错误中断状态寄存器(ERRSTAT)      |     |

| 15.3.8 错误中断使能寄存器(ERRSTAT)      |     |

| 15.3.9 状态寄存器 (STAT)            |     |

| 15.3.10 控制寄存器(CTL)             |     |

| 15.3.11 地址寄存器(ADDR)            |     |

| 15.3.12 帧号寄存器(FRMNUML,FRMNUMH) |     |

| 15.3.13 端点控制寄存器(EPCTLn, n=0-6) |     |

| 15.4 功能描述                      |     |

| 15.4.1 模块描述                    |     |

| 15.4.2 缓冲区描述表(BDT)             |     |

| 15.4.5 起始帧处理                   |     |

| 15.4.6 挂起/恢复                   | 210 |

| 15.4.6.2.1 主机初始恢复              | 210 |

| 15.4.7 复位                      | 211 |

| 15.4.8 中断                      |     |

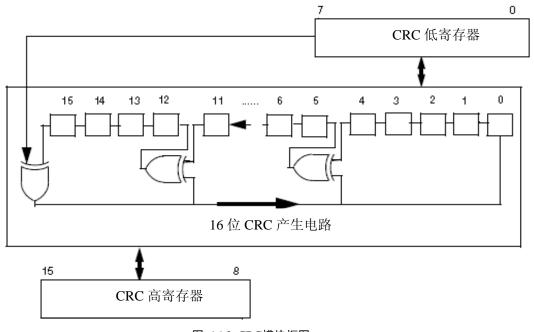

| 第十六章 环冗余校验发生器(S08CRCV2)        | 213 |

| 16.1 引言                        | 213 |

| 16.1.1 特性                      |     |

| 16.1.2 操作模式                    |     |

| 16.1.3 模块图                     |     |

| 16.2 扩展信号描述                    |     |

| 16.3 寄存器定义                     |     |

| 16.3.1 内存映射                    |     |

| 16.3.2 寄存器描述                        | 216 |

|-------------------------------------|-----|

| 16.4 功能描述                           | 217 |

| 16.4.1 ITU-T(CCITT)使用建议以及期望的 CRC 结果 | 217 |

| 16.5 初始化信息                          | 218 |

| 第十七章 开发支持                           | 219 |

| 17.1 引言                             | 219 |

| 17.1.1 特性                           | 219 |

| 17.2 背景调试控制器(BDC)                   | 220 |

| 17.2.1 BKGD 引脚描述                    | 220 |

| 17.2.2 通信详细介绍                       | 221 |

| 17.2.3 BDC 命令                       | 222 |

| 17.2.4 BDC 硬件断点                     |     |

| 17.3 片上调试系统(DBG)                    | 225 |

| 17.3.1 比较器 A 和 B                    | 225 |

| 17.3.2 总线捕获信息和 FIFO 操作              | 225 |

| 17.3.3 流变化信息                        | 226 |

| 17.3.4 标记 vs.强制断点和触发器               | 226 |

| 17.3.5 触发模式                         | 226 |

| 17.3.6 硬件断点                         | 228 |

| 17.4 寄存器定义                          | 228 |

| 17.4.1 BDC 寄存器和控制位                  | 228 |

| 17.4.2 系统背景调试强制复位寄存器(SBDFR)         | 230 |

| 17.4.3 DBG 寄存器和控制位                  | 230 |

# 第一章 导言

# 1.1 芯片概述

MC9S08JS60 系列 MCU 是 HCS08 家族成员中低成本、高性能的 8 位微处理器。家族中所有的 MCU 使用增强型 HCS08 内核,可以根据需要选取使用具有不同的模块,存储器大小,存储器类型和封装类型。

注:

MC9S08JS16/MC9S08JS8 和 MC9S08JS16L/MC9S08JS8L 唯一的区别在于 MC9S08JS16 和 MC9S08JS8 支持 USB 引导程序在电压高于 3.9V 时工作,而 MC9S08JS16L 和 MC9S08JS8L 支持 USB 引导程序在电压等于 3.3V 时工作。

当使用 MC9S08JS16L 和 MC9S08JS8L 的 USB 引导程序功能时, 应禁止内部 USB 电压调节器并向  $V_{USB33}$  引脚输入 3.3V 电源。

表 1-1 总结了在 MC9S08JS16 系列中芯片的每个封装类型的可用外设。

| 特点          | MC9S08JS8/ MC9S08JS8L |       | MC9S08JS16/ MC9S08JS16L |               | S08JS16L |           |

|-------------|-----------------------|-------|-------------------------|---------------|----------|-----------|

| 封装          | 24引脚                  | QFN : | 20引脚 SOIC               | 24引脚 QFN 20引脚 |          | 20引脚 SOIC |

| Flash大小(字节) |                       | 8192  |                         | 16384         |          |           |

| RAM大小(字节)   |                       | 512   |                         | 512           |          |           |

| USB RAM(字节) |                       | 256   |                         | 256           |          |           |

| ACMP        |                       | 有     |                         | 256           |          |           |

| ADC         |                       | 12通道  |                         | 有             |          |           |

| IIC         | 有                     | 8通道   | 8通道                     | 12通道          | 8通道      | 8通道       |

| IRQ         |                       | 有     |                         | 有             |          |           |

| KBI         | 8                     |       | 有                       |               |          |           |

| SCI         | 有                     |       | 8                       | 7             | 7        |           |

| SPI         | 有                     |       | 有                       |               |          |           |

| MTIM        | 有                     |       | MTIM 有 有                |               |          |           |

| TPM通道       | 2                     |       | 2                       |               |          |           |

| USB         | 有                     |       |                         | 有             |          |           |

| CRC         | 有                     |       | 有                       |               |          |           |

| I/O引脚       | 14(2个只能输出)            |       | ]                       | 14(2个只能输      | 1出)      |           |

表1-1 MC9S08JS16系列各MCU封装的特点

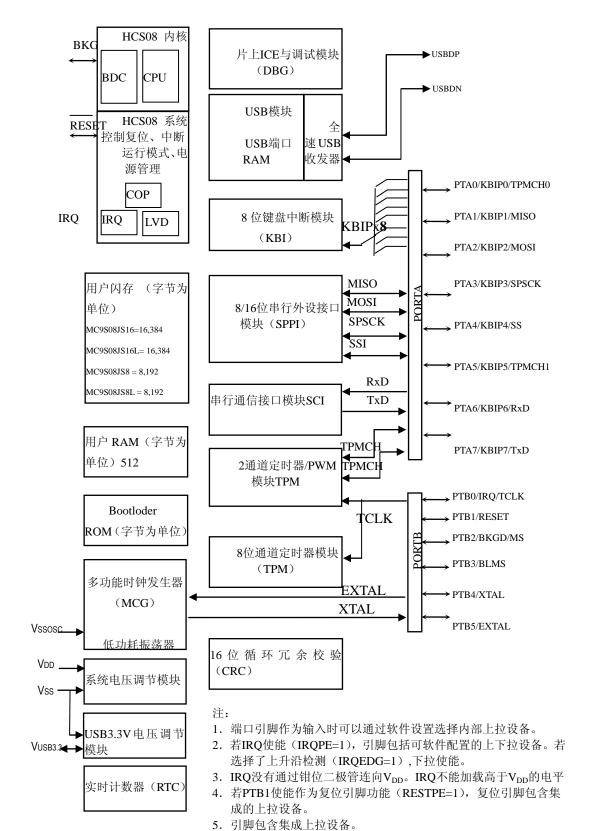

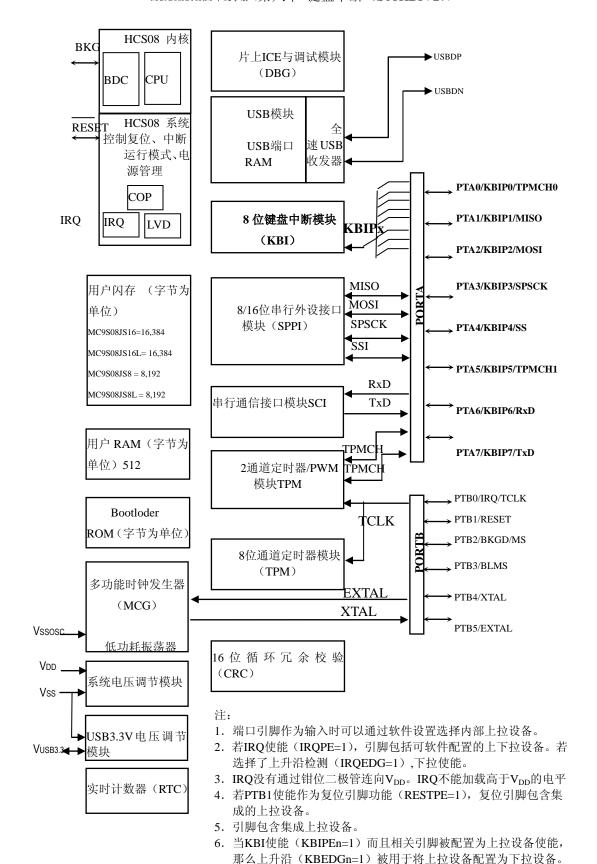

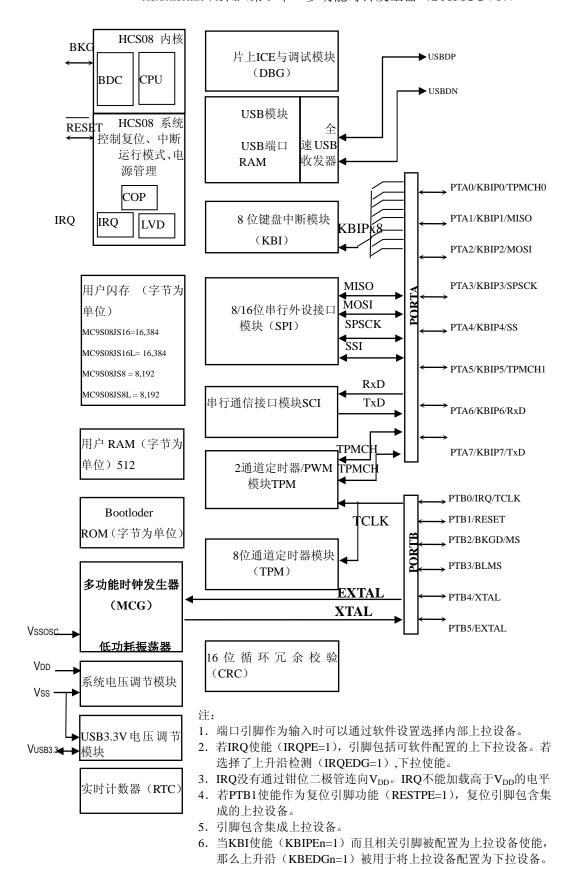

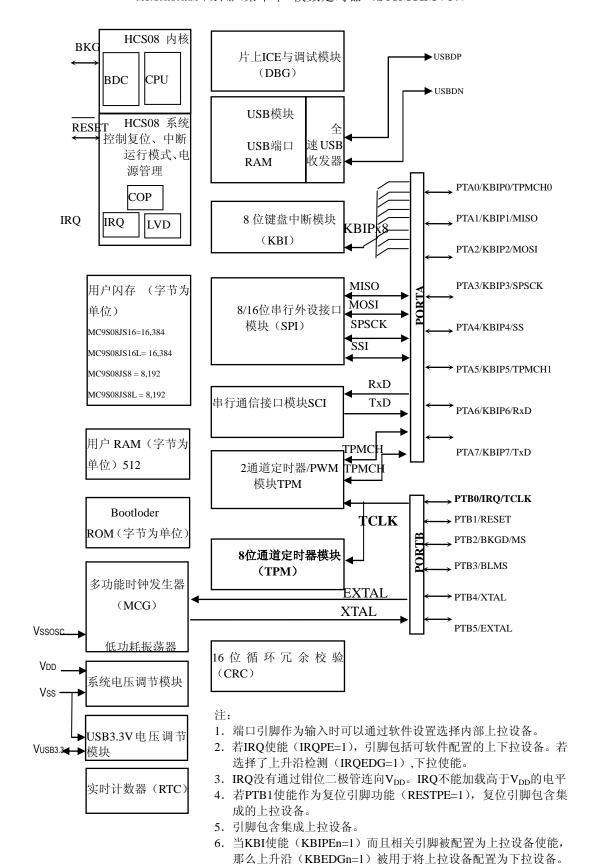

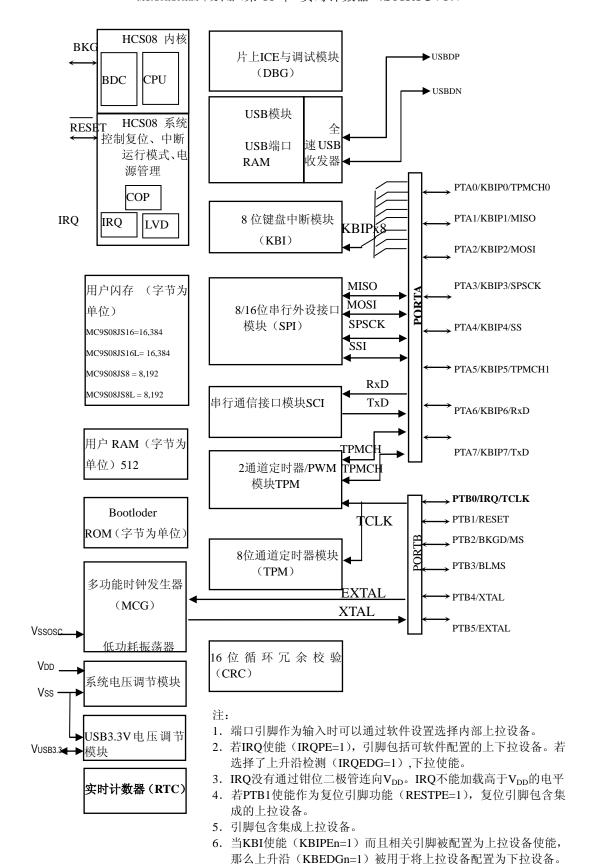

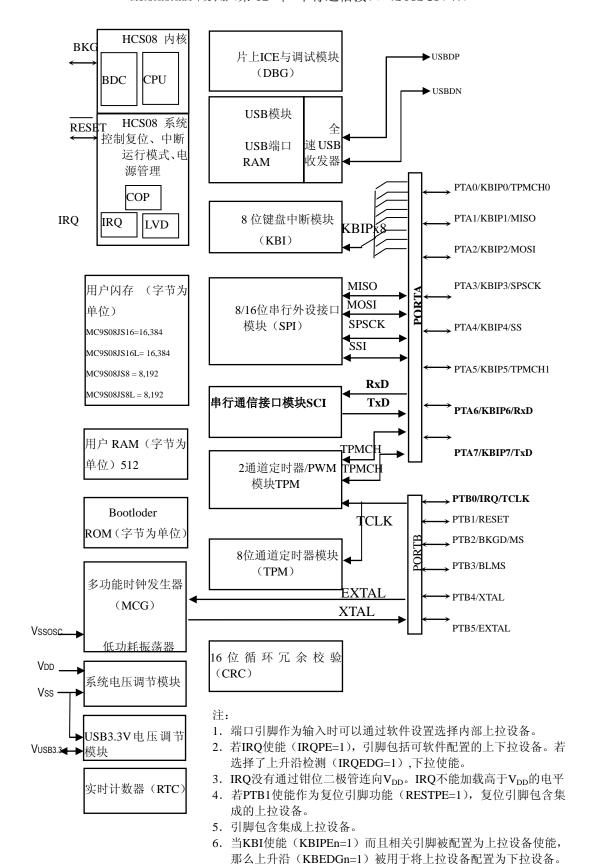

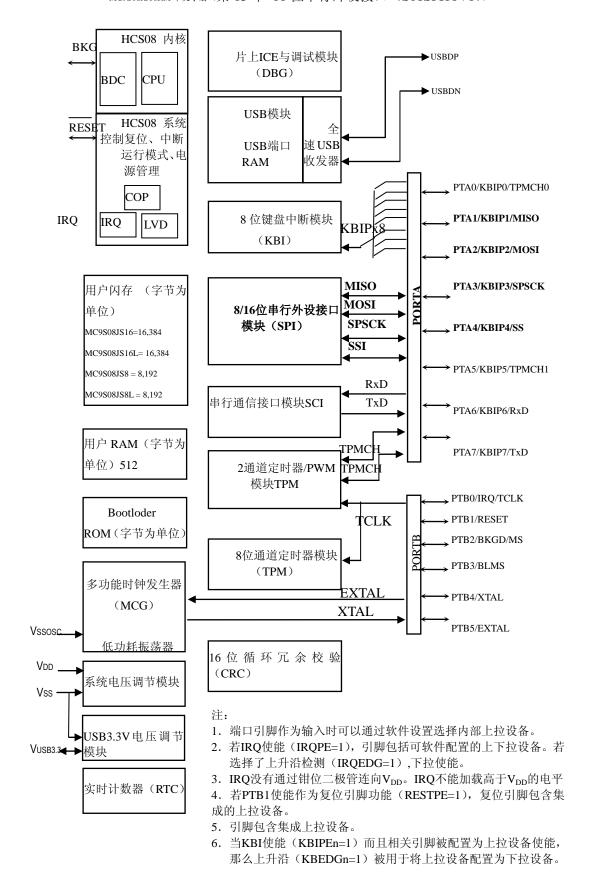

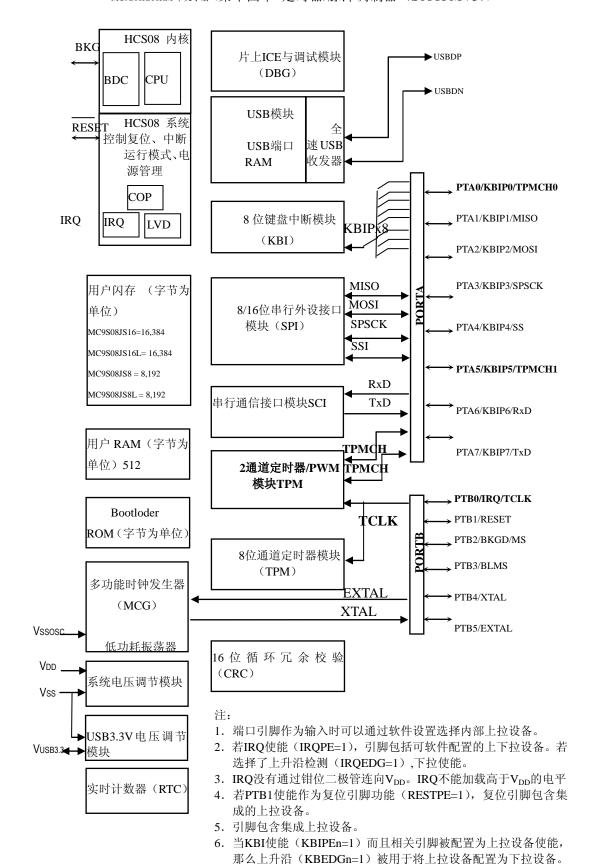

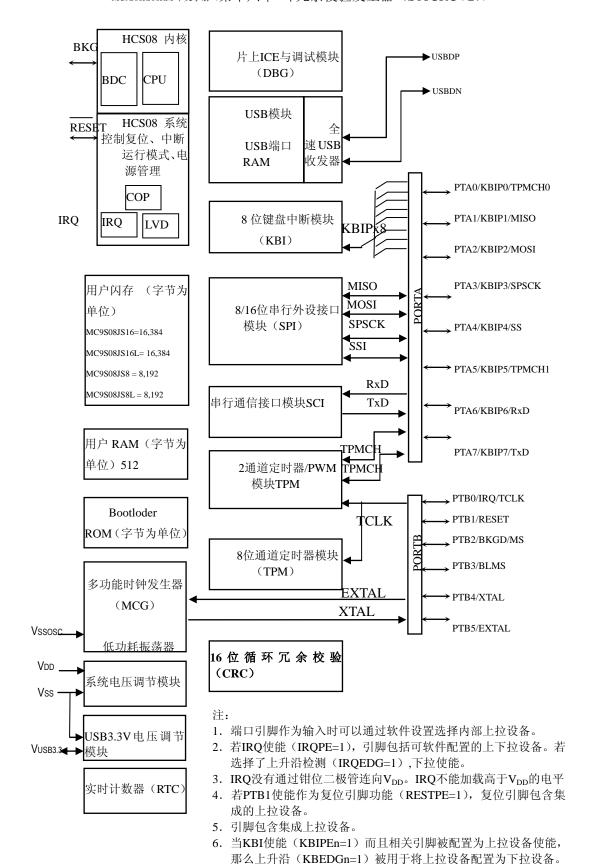

## 1.2 MCU框图

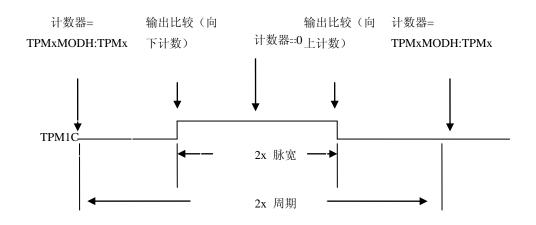

图 1-1 的框图给出了 MC9S08JS16MCU 的结构。

6. 当KBI使能(KBIPEn=1)而且相关引脚被配置为上拉设备使能, 那么上升沿(KBEDGn=1)被用于将上拉设备配置为下拉设备。

图 8-1. MC9S08JS16系列框图

表 1-2 列出了片内模块的功能版本。

表1-3片内模块的版本

| 模块         |         | 版本 |

|------------|---------|----|

| 中央处理器      | (CPU)   | 2  |

| 模拟比较器      | (ACMP)  | 2  |

|            | Ę       | 1  |

| (MCG)      |         | 1  |

| 实时计数器      | (RTC)   | 1  |

| AD转换器      | (ADC)   | 1  |

| 串行通讯接口     | (SCI)   | 4  |

| 16位串行外设接口  | (SPI16) | 1  |

| 模计时器       | (MTIM)  | 1  |

| 计时器脉冲宽度调制器 | (TPM)   | 3  |

| 通用串行总线     | (USB)   | 1  |

| 循环冗余校验发生器  | (CRC)   | 2  |

| 调试模块       | (DBG)   | 2  |

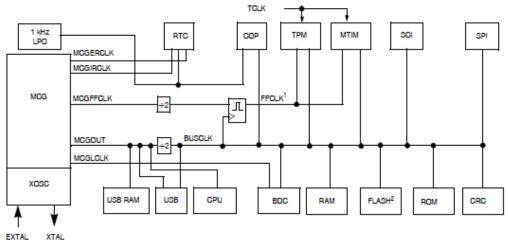

# 1.3 系统时钟分布

TCLK——TPM 和 MTIM 的外部输入时钟源,并且在第十四章,"计时器脉冲宽度调制器(S08TPMV3)"以 TPMCLK 被提到。

- 1 固定频率时钟(FFCLK)被内部同步到总线时钟,且不能超过总线时钟频率的一半。

- 2 FLASH和EEPROM对写入和擦除操作有频率要求,见MC9S08JS16系列手册获得详细说明。

图1-2 系统时钟分布框图

MCG 提供了如下时钟源:

- MCGOUG——该时钟源被用于 CPU, USB RAM 和 USB 模块的时钟,除以二即得到外设总线时钟频率(BUSCLK)。MCG 控制寄存器中的控制位决定了连接三个时钟源中的哪一个。

- ——内部参考时钟

- ——外部参考时钟

- ——频率锁相环(FLL)或者 PLL 锁相环输出

- 参考第九章, "多功能时钟发生器(S08MCGV1),"参考设置 MCGOUT 时钟的细

节。

#### MC9S08JS16RM 中文手册 (第一章 导言)

- MCGLCLK——该时钟源由 MCG 的数控振荡器(DCO)产生。当系统内总线时钟频率较低时可以用高级工具选择这个内部自时钟来加速 BDC 通讯。

- MCGIRCLK——这是内部参考时钟并且可以被选作实时计数器(RTC)的时钟源。第九章,"多 功能时钟发生器(S08MCGV1),"详细解释了MCGIRCLK。第十一章,"实时计数器(S08RTCV1)," 给出了更多关于MCGIRCLK使用方面的信息。

- MCGERCLK——这是外部参考时钟并且可被选作实时计数器模块的时钟源。9.4.6 节,"外部参考时钟",详细说明了 MCGERCLK。第十一章,"实时计数器(S08RTCV1)",给出了关于 MCGERCLK 应用于该模块的详细信息。

- MCGFFCLK——这个时钟源频率与 BUSCLK 同步以后除以 2 用以产生 FFCLK。它可以被选作 TPM 或 MTIM 模块的时钟源。MCGFFCLK 的频率由 MCG 的具体设置决定。参考 9.4.7 节,"固定频率时钟",获得更多细节。

- LPO 时钟——这个时钟由一个完全独立于 MCG 模块的内部低功耗振荡器产生。LPO 时钟可被选作 RTC 或 COP 模块的时钟源。第十一章,"实时计数器(S08RTCV1),"和 5.4 节,"计算机正常操作监控模块(COP)看门狗,"给出了 LPO 时钟应用于这些模块的详细说明。

- TPMCLK——TPMCLK 是 TPM 或 MTIM 模块的可选外部时钟源。TPMCLK 的频率必须限制在总线频率的 1/4 以内来保证同步。参考第十四章,"计时器脉冲宽度调制器(S08TPMV3),"获得更多信息。

# 第二章 引脚和连接

# 2.1 简介

这一章描述了连接到各封装引脚的信号。内容包括引脚布局图,信号性能表,以及对信号的详细描述。

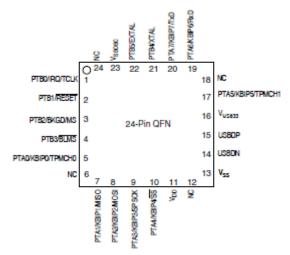

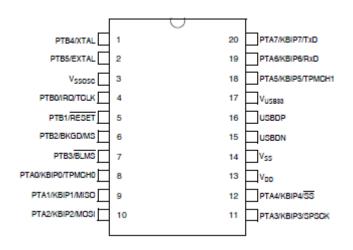

# 2.2 芯片引脚布局

图2-1 MC9S08JS16系列24引脚QFN封装

图2-2 MC9S08JS16系列20引脚SOIC封装

# 2.3 推荐系统连接

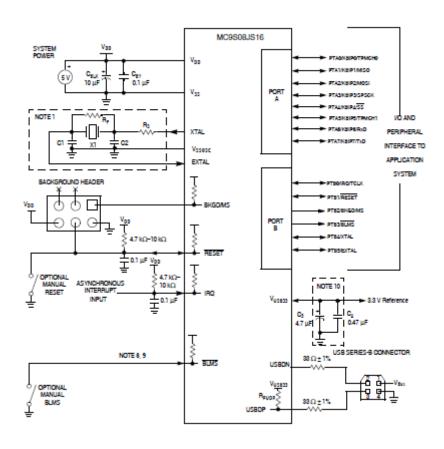

图 2-3 显示了几乎所有 MC9S08JS16 系列应用系统通用的引脚连接。

注:

- 1.如果使用MCG内部时钟则不需要外部晶振电路。USB操作需要外部晶振。

- 2.XTAL和EXTAL引脚和PTB4,PTB5一样。

- 3. EMC敏感应用推荐在RESET和IRQ上接RC滤波器。

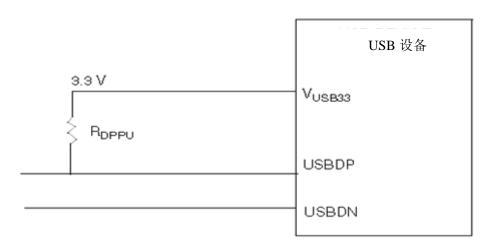

- 4  $R_{PUDP}$ 只用于全速USB。框图显示了片内调节器和 $R_{PUDP}$ 被使能时的设置。电压调节器输出用于 $R_{PUDP}$ 。当在USBDP上接外部上拉电阻时, $P_{RUDP}$ 可以选择性被禁止。

- 5.V<sub>BUS</sub>是从上游端口提供的5V电压用于USB操作。

- 6.USBDP和USBDN由3.3V调节器供电。

- 7.USB操作时推荐一个2MHZ或4MHZ的外部晶振。

- 8.BLMS引脚有装载限制,不在该引脚上连接任何电容。

- 9.如果在PTB2/PTB3上游外部上拉电阻,引脚被安排为输出引脚。否则会在引脚上有电流消耗(10K欧姆有 0.5mA)。PTB2/PTB3上负载必须小于50PF。

- 10.如果使用V<sub>USB33</sub>作为电源,需要一个外部电容。

图2-3 基本系统连接

# 2.3.1 电源(VDD, VSS, VSSOSC, VUSB33)

V<sub>DD</sub>和 V<sub>SS</sub>是 MCU 主要电源供应引脚,该电源给所有 I/O 缓冲电路和一个内部电压调节器供电。内部电压调节器将调节后的低压电源提供给 CPU 和 MCU 其它内部电路。

一般情况下,实际应用系统中电源引脚接两个独立的电容。在这种情况下,应该选用一个大容量电解电容器来为全体系统提供大电量存储,如  $10\mu F$  的钽电容,另外一个选用  $0.1\mu F$  的陶瓷旁路电容,尽可能的靠近配对的  $V_{DD}$  和  $V_{SS}$  电源引脚,用以抑制高频噪声。 MC9S08JS16 系列都有一个  $V_{SSOSC}$  引脚。这个引脚应连接到系统的接地平面或低阻抗连接到主  $V_{SS}$  引脚。

V<sub>USB33</sub> 连接内部 USB 3.3V 电压调节器。第十五章,"通用串行总线设备控制器

(S08USBV1)",全面介绍了 V<sub>USB33</sub> 电源引脚。

#### 2.3.2 振荡器(XTAL,EXTAL)

复位过后,MCU 使用内部发生的时钟,这个时钟源由 MCG 模块产生。想了解更多关于 MCG 的信息,请参考第九章,"多功能时钟发生器(S08MCGV1)"。

这个 MCU 的振荡器(XOSC)是一个皮尔斯振荡器,可容纳一个晶体或陶瓷谐振器,除了一个晶体或陶瓷的谐振器,一个外接振荡器还可以被连接到 EXTAL 输入引脚。

RS(使用时)与 RF 是低电感电阻,如碳电阻。线绕电阻和一些金属膜电阻器,电感太大。C1 和 C2 通常应是专门为高频率应用设计的高品质的陶瓷电容器。

RF 是用来提供一个偏置的路径的电阻,来保证在晶振启动时,EXTAL 的输入在其线性范围内且其阻值一般不是很重要。典型的系统 RF 阻值为  $1M\Omega$  至  $10M\Omega$  。阻值较高会对湿度比较敏感,阻值较低会减少增益并有可能阻止启动(在极端情况下)。

C1 和 C2 通常在 5pF 至 25pF 范围之间,选择时要与具体的晶振或谐振器相匹配。在选择 C1 和 C2 时务必要考虑到印刷电路板 (PCB) 和 MCU 引脚的电容。晶振制造商通常要指定一个负载电容,值等于 C1 和 C2 (电容值通常相等) 串联的串联值。作为首选的近似值,为每个振荡器引脚 (EXTAL 和 XTAL) 使用约 10pF 的电容作为引脚和 PCB 的连接电容。

### 2.3.3 RESET 引脚

经过上电复位(POR),PTB1/RESET 引脚被缺省指定为一个通用输入端口引脚,PTB1。

将 SOPT1 中的 RSTPE 置 1 可以将该引脚设为包含了一个内接上拉设备的 RESET 引脚。之

后,该引脚将一直作为 RESET 引脚直到下一个 LVD 或 POR。当被使能时, RESET 引脚可以被用来在该引脚被拉低时使 MCU 从一个外部源中复位。

内部上电复位和低电压复位电路通常使得系统不需要外部复位电路。引脚通常是连接到标准的 6 引脚背景调试连接器,所以一个开发系统可以直接复位 MCU 系统。如果需要,可以通过添加一个简单的接地开关来增加一个外部手动复位装置(拉低复位引脚来强迫复位)。

当有非 POR 复位启动时 (无论来自外部信号还是系统内部), RESET 引脚的电平会被 拉低大约 66 个总线周期, 然后被释放。复位电路解码复位事件并通过置位系统控制复位状态寄存器 (SRS) 相应的位将其记录下来。

注:

加载在内接上拉RESET 引脚上的电压测量值比 $V_{DD}$ 低。连接到该引脚上的内接门电路被拉至 $V_{DD}$ 。

如果要求将 RESET 引脚拉至 Vpp 水平,则必须使用外接上拉设备。

注:

在 EMC 敏感的应用中,推荐在复位引脚(允许)上配置一个外部 RC 滤波器。(图 2-3)

# 2.3.4 背景/模式选择(BKGD/MS)

在上电复位 (POR) 或是背景调试强制复位 (见 5.7.3 节,"系统背景调试强制复位寄存器 (SBDFR),"获得更多细节)中,PTB2/BKGD/MS 引脚作为一个模式选择引脚。复位后,

该引脚立即作为背景引脚被用于背景调试通信。当作为 BKGD/MS 引脚时(BKGDPE=1),该引脚自动包含一个内部上拉电阻。

当 SOPT1 中的 BKGDPE 被置 1 时,背景调试通信功能被允许。BKGDPE 在任何 MCU 复位后都会被置 1,在使用任何 PTB2/BKGD/MS 引脚备选功能时该位必须被清零。

若这个引脚上没有任何连接,则 MCU 在复位的上升沿进入正常的操作模式。如果调试系统被连接到 6 引脚的标准背景调试接口,它可以在复位上升沿时保持 BKGD/MS 为低电平,强制 MCU 进入背景模式。

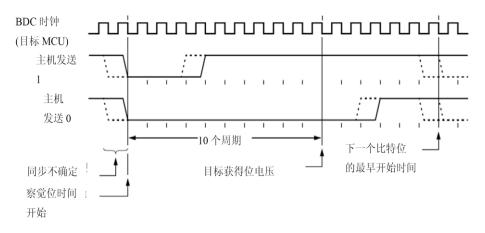

BKGD 引脚主要用于背景调试控制器(BDC)通讯使用,遵循自定义协议,该协议规定每传送一个位使用目标 MCU 的 16 个 BDC 时钟周期。目标 MCU 的 BDC 时钟频率可以和总线时钟频率一样,因此不要将任何大的电容和 BKGD/MS 引脚相连,否则会干扰背景串行通信。

虽然 BKGD 引脚是一个伪开漏引脚,但是背景调试通信协议提供了简短的,主动驱动,高加速脉冲以确保快速上升时间。电缆的小电容和内部上拉电阻的绝对值对 BKGD 引脚上的上升沿和下降沿几乎不起任何作用。

注: 在 IRQ 或 RESET 功能被允许前,要在功能引脚上允许 GPIO 上拉并且等待 2μs。否则 IRQ 或

RESET 设置可能会失败。

### 2.3.5引导程序模式选择(BLMS)

在上电复位(POR)过程中,CPU 探测作为模式选择引脚的 PTB3/BLMS引脚的状态。 当逻辑为低且 BKGD/MS 没有被拉低时,CPU 进入引导程序模式。在上电复位(POR)过程中,接到 PTB3/BLMS引脚的内部上拉设备自动被使能。复位上升过后,该引脚立刻作为通用输出引脚且内部上拉设备自动被禁止。

### 2.3.6 USB数据引脚(USBDP,USBDN)

USBDP (D+) 和 USBDN (D-) 引脚是在 USB 物理层 (PHY) 模块内接全速数据通讯的模拟输入/输出线路。R<sub>PUDP</sub>是 USBDP 引脚的可选上拉电阻。

# 2.3.7 GPIO及外设端口

MC9S08JS16 系列 MCU 共支持 14 个通用 IO 引脚,包含两个与片内外设复用的单输出引脚,(定时器,串行 I/O,键盘中断,etc)。

当一个引脚被设置为一个通用输出引脚或外设输出引脚时,程序可以设置驱动强度和禁止或允许速率转换控制。当一个引脚被设置为一个通用输入引脚或外设输入引脚时,程序可以允许上拉设备。

要详细了解如何将这些引脚定义为输入/输出引脚,请参考第六章,"并行输入/输出"。要了解哪种情况下以及怎样将这些引脚定义为外设引脚,请参考相关章节。

复位过后,所有的引脚除了单输出引脚(PTB2/BKGD/MS,PTB3/BLMS)都被设置为高阻抗通用输入引脚,上拉设备被禁止。

表2-1 引脚功能及封装引脚数

| 引脚数<br>(封装) |                  | 《——最低 | 优先级   | ——》最高             |

|-------------|------------------|-------|-------|-------------------|

|             | 到表)<br>20 (SOIC) | 端口引脚  | A14.1 | Alt 2             |

| 24 (QFN)    |                  |       | Alt 1 |                   |

| 1           | 4                | PTB0  | IRQ   | TCLK              |

| 2           | 5                | PTB1  |       | RESET             |

| 3           | 6                | PTB2  | BKGD  | MS                |

| 4           | 7                | PTB3  |       | BLMS              |

| 5           | 8                | PTA0  | KBIP0 | TPMCH0            |

| 6           | _                | NC    |       |                   |

| 7           | 9                | PTA1  | KBIP1 | MISO              |

| 8           | 10               | PTA2  | KBIP2 | MOSI              |

| 9           | 11               | PTA3  | KBIP3 | SPSCK             |

| 10          | 12               | PTA4  | KBIP4 | SS                |

| 11          | 13               |       |       | $V_{\mathrm{DD}}$ |

| 12          | _                | NC    |       |                   |

| 13          | 14               |       |       | $V_{SS}$          |

| 14          | 15               |       |       | USBDN             |

|             | 引脚数<br>封装)       | 《——最低 | 优先级   | ——》最高             |

| 15          | 16               |       |       | USBDP             |

| 16          | 17               |       |       | $V_{USB33}$       |

| 17          | 18               | PTA5  | KBIP5 | TPMCH1            |

| 18          | _                | NC    |       |                   |

| 19          | 19               | PTA6  | KBIP6 | RxD               |

| 20          | 20               | PTA7  | KBIP7 | TxD               |

| 21          | 1                | PTB4  | XTAL  |                   |

| 22          | 2                | PTB5  | EXTAL |                   |

| 23          | 3                |       |       | $V_{SSOSC}$       |

| 24          | _                | NC    |       |                   |

注:

当一个可选功能首先被允许时,可能会使该模块有一个杂乱的沿。用户程序必须在中断允许前将所有相关标志位清零。表 2-1 显示了如果有多个模块被允许它们之间的优先级。最高优先级的模块将会控制引脚。在一个较低优先级功能已经允许的情况下选择一个较高优先级的引脚功能将会使低优先级的模块有杂乱的沿。一个模块被允许前所有共享该引脚的模块必须被禁止。

# 第三章 操作模式

# 3.1 简介

本章将描述 MC9S08JS60 的操作模式。同时描述进入各种模式、退出各种模式和各种模式中的功能。

#### 3.2 特性

用于代码设计的激活背景模式

等待模式:

CPU 暂停,以节省电力

系统时钟运行

保持全电压调节

停止模式: CPU 和总线时钟停止

STOP2—内部电路部分掉电,RAM和 USB RAM的内容保留

STOP3—为快速恢复,所有内部电路不掉电;RAM 和 USB RAM 以及寄存器内容保留

#### 3.3 运行模式

这是 MC9S08JS60 系列在一般情况下的操作模式。在 MCU 离开复位时,若 BKGD/MS 为高电平,则进入此模式。在这种模式下复位后,CPU 从存储器的 0xFFFE:0xFFFF 中取出程序首地址,执行内存中的代码。

# 3.4 激活背景模式

激活背景模式功能由 HCS08 内核中的背景调试控制器(BDC)管理。在软件开发期间 BDC 连同片内在线仿真器 (ICE) 调试模块 (DBG) 一起提供各种方式来分析 MCU 操作 (见5.7.3 节,"系统背景调试强制复位寄存器(SBDFR)")

进入激活背景模式的五种方式:

在 POR 过程中或紧接着背景调试强制复位之后当 BKGD /MS 引脚为低电平时

当 BKGD 引脚接收到 BACKGROUND 命令时

当 BGND 指令被执行时

当遇到 BDC 断点时

当遇到 DBG 断点时

在进入激活背景模式后,CPU 处于一个暂停状态,等待串行后台命令,而不是执行用户应用程序的指令。

后台命令的两种类型:

非插入命令,定义为可在用户程序运行时发出的命令。当 MCU 在运行模式下时,非插入命令可经由 BKGD 引脚发出。当 MCU 在激活背景模式下也可执行非插入命令。非插入命令包括:

存储器访问命令

存储器访问状态命令

BDC 寄存器访问命令

BACKGROUND 命令

激活背景命令,只有当 MCU 在激活背景模式下才可以执行。激活背景命令,包括:读/写 CPU 寄存器

单步调试指令

退出激活背景模式,返回用户应用程序(GO)

激活背景模式通常用于 MCU 第一次在运行模式下运行之前,向 Flash 程序存储器写入 引导程序或用户程序。当 MC9S08JS60 系列 FREESCALE 半导体出厂时,除非有特别指明, Flash 存储器默认为擦除,因此在运行模式下没有程序可以执行,直到 Flash 存储器初次被编程。激活背景模式也可用于在 Flash 存储器已经写入程序后,对其进行擦除和重新写入程序。

有关激活背景模式的更多信息可见第 17 章"开发支持"。

#### 3.5 等待模式

等待模式由执行 WAIT 指令进入。在执行 WAIT 指令时,CPU 处于一个没有时钟的低功耗状态。当 CPU 的进入等待模式时,CCR 中的 I 位被清零,允许中断。当一个中断请求发生时,CPU 退出等待模式,恢复正常处理,开始堆栈操作,运行相应的中断服务程序。 而MCU 在等待模式,对可用的背景调试命令有一些限制。当 MCU 在等待模式下,只有BACKGROUND 命令和存储器访问状态命令可用。存储器访问状态命令不容许存储器访问,但它们会报告一个错误,表明 MCU 处于停止或等待模式。BACKGROUND 命令可以将 MCU 从等待模式唤醒,进入激活背景模式。

### 3.6 停止模式

当系统选项寄存器中的 STOPE 位置位时,执行到 STOP 指令系统就进入两种停止模式的一种。在两种停止模式下,总线和 CPU 时钟都被暂停。MCG 模块可以被设置为离开内部参考时钟运行。更多的有关信息可见第九章,"多功能时钟发生器(S08MCGV1),"。

一些为低电压 (1.8 到 3.6V) 操作设计的 HCS08 芯片还包含 STOP1 模式。MC9S08JS16 系列 MCU 不包含 STOP1 模式。

表 3-1 显示了所有影响停止模式选择的控制位以及各种情况下模式的选择。在执行一个 STOP 指令后系统进入一个选定的模式。

| ST  | EN               | L      | L     | PP | /古.L.+共}                     |  |   |  |                      |

|-----|------------------|--------|-------|----|------------------------------|--|---|--|----------------------|

| OPE | BDM <sup>1</sup> | VDE    | VDSE  | DC | 停止模式<br>                     |  |   |  |                      |

| 0   | v                |        | -     |    | v                            |  | v |  | 停止模式被禁止,执行STOP指令会导致非 |

|     | X                | X      |       | X  | 法操作码复位                       |  |   |  |                      |

| 1   | 1                | X      |       | X  | 进入STOP3 <sup>2</sup> , BDM允许 |  |   |  |                      |

| 1   | 0                | 两~     | 两个位都必 |    | 进入STOP3,激活电压调节器              |  |   |  |                      |

| 1   | U                | 须:     | 须为1   |    | 近八31013,成冶电压加刊品              |  |   |  |                      |

| 1   | 0                | 任意一位为0 |       | 0  | STOP3                        |  |   |  |                      |

| 1   | 0                | 任意     | 5一位为0 | 1  | STOP2                        |  |   |  |                      |

表3-1 停止模式选择

<sup>1</sup> ENBDM 位于 BDCSCR 中,仅仅能通过 BDC 命令进入,见 14.4.1.1 节,"BDC 状态与控制寄存器(BDCSCR)"。

2 当处于 STOP3 模式且 BDM 允许时,因为内部时钟允许运行, $S_{IDD}$  会接近  $R_{IDD}$  水平。

#### 3.6.1 STOP3模式

在表 3-1 所示的条件下,执行 STOP 指令进入 Stop3 模式。所有的内部寄存器和逻辑,RAM 的内容,和 I/O 引脚状态都被保持。

STOP3 可以通过 RESET 方式退出,或由以下某项中断源退出:实时中断 (RTC), USB 恢复中断,LVD,IRQ,KBI,或 SCI。

如果 STOP3 是以 RESET 引脚方式退出的,那么获取复位向量后,MCU 会复位,操作会恢复。如果因内部中断源退出,MCU 就获取适当的中断向量。

#### 3.6.1.1 停止模式下LVD使能

当供应电压下降到 LVD 电压值以下时,LVD 系统能够产生中断或复位。如果在 CUP 执行 STOP 指令时 LVD 在停止模式中被允许(SPMSC1 中的 LVDE 和 LVDSE 都被设置为 1),则电压调节器在停止模式过程中保持激活状态。如果在停止模式中允许 LVD 的情况下用户试图进入 SPOP2,MCU 会进入 STOP3 模式。

当 MCGC2 中的 RANGE 位被置 1 时,为了可以在一个外部参考时钟下操作 XOSC,进入 STOP3 模式时 LVD 必须被设置为允许。

注:

为了得到 USB 低挂起电流,在进入 USB 挂起模式之前,我们必须将 MCGC2 中的 ERCLKEN 何 EREFSTEN 置 1,但是在 STOP3 模式中将 LVD 禁止。

#### 3.6.1.2 停止模式下激活的BDM使能

如果 BDCSCR 的 ENBDM 位被置位,则从运行模式进入激活背景模式被允许。第 17 章"开发支持"中描述了该寄存器。当 CPU 执行 STOP 指令时,如果 ENBDM 被置位,这样当 MCU 进入到停止模式后背景调试逻辑的系统时钟仍然在工作,所以背景调试通信仍然是可能的。此外,电压调试器没有进入低功耗待机状态,而是保持满负荷工作中。如果用户试图在 ENBDM 置位的情况下进入 STOP2,MCU 将进入 STOP3 。

大部分后台命令在停止模式下是无效的。存储器访问状态命令不允许访问存储器,但它们会报告一个错误,表明 MCU 在停止或等待模式。如果 ENBDM 置位,BACKGROUND 指令可以用于将 MCU 从停止模式中唤醒进入激活背景模式。一旦进入背景调试模式后,所有后台命令都可用。

# 3.6.2 STOP2模式

在如表 3-1 的条件下执行一条 STOP 指令即可进入 STOP2 模式。大多数 MCU 的内部电路在 STOP2 时都处于掉电状态,除了 RAM 以外。进入 STOP2 模式,所有的 I/O 引脚控制信号被锁定,以在 STOP2 模式期间保留引脚状态。

离开 STOP2 模式可以依靠下面两个唤醒引脚中任意一个: RESET 或 IRQ。当一个程序使用 STOP2 模式状态,RESET 或 IRQ 引脚必须事先预设置为一个输入引脚来进入 STOP2

模式。一个模拟连接从RESET 或 IRQ 垫连接到电源管理控制器唤醒引脚——如果该引脚被设置为 GPIO 输出引脚,它可以防止 STOP2 的操作发生。

另外,RTC 中断如果被允许,它也可以将 MCU 从 STOP2 模式中唤醒。将系统从 STOP2 模式唤醒后,MCU 将作为上电复位(POR)启动:

● 所有的模块控制和状态寄存器将被复位

- 如果 V<sub>DD</sub>低于 LVD 的跳变点(低跳变点的选择取决于 POR),LVD 复位功能将被允许,MCU 将保持在复位状态。

- CPU 获得复位向量

除上述以外,从 STOP2 模式被唤醒后, SPMSC2 的 PPDF 位被置位。这个标志被用来指向用户代码进入一个 STOP2 的一个恢复例程。PPDF 保持置位、I/O 引脚状态保持锁存,直到逻辑 1 写入 SPMSC2 的 PPDACK 位。

进入 STOP2 模式前,要保持被设定为通用 I/O 引脚的 I/O 状态,用户必须在写 PPDACK 位之前将已被保存在 RAM 上的 I/O 端口寄存器中的内容写回端口寄存器。在写 PPDACK 之前,如果端口寄存器没有存储来自 RAM 的内容,那么在写 PPDACK 位时,I/O 引脚将转换到其复位状态。

引脚被设定为外设 I/O 引脚,在写 PPDACK 位之前,用户必须重新设定接口到该引脚的外设模块。在写 PPDACK 之前,如果外设模块未启用,当 I/O 锁存开放时,引脚将被其相关的端口控制寄存器控制。

## 3.6.3 停止模式下片内外设模块

当 MCU 进入任何 STOP 模式,到内部外设模块的系统时钟都被关闭。甚至在例外情况下(ENBDM=1),背景调试逻辑的时钟继续运行,外设系统时钟也会停止以降低功耗。停止模式下系统行为的具体信息请参阅 3.6.2 节,"STOP2 模式",和 3.6.1,"STOP3 模式"。表 3-4 给出了停止模式下的行为。

| AL VII.      | 模式    |                                       |  |  |  |  |

|--------------|-------|---------------------------------------|--|--|--|--|

| 外设           | STOP2 | STOP3                                 |  |  |  |  |

| CPU          | 关闭    | 待机                                    |  |  |  |  |

| RAM          | 待机    | 待机                                    |  |  |  |  |

| Flash        | 关闭    | 待机                                    |  |  |  |  |

| 并行端口寄存器      | 关闭    | 待机                                    |  |  |  |  |

| MCG          | 关闭    | 可选 <sup>1</sup>                       |  |  |  |  |

| RTC          | 可选4   | 可选 <sup>2</sup>                       |  |  |  |  |

| SCI          | 关闭    | 待机                                    |  |  |  |  |

| MTIM         | 关闭    | 待机                                    |  |  |  |  |

| SPI          | 关闭    | ————————————<br>待机                    |  |  |  |  |

| TPM          | 关闭    | ————————————<br>待机                    |  |  |  |  |

| 系统电压调节器      | 关闭    | ————————————————————————————————————— |  |  |  |  |

| XOSC         | 关闭    | 可选3                                   |  |  |  |  |

| I/O引脚        | 保持状态  | 保持状态                                  |  |  |  |  |

| USB(SIE和PHY) | 关闭    | 可选 <sup>4</sup>                       |  |  |  |  |

| USB 3.3V 调节器 | 关闭    | 待机                                    |  |  |  |  |

| USB RAM      | 待机    | 待机                                    |  |  |  |  |

| CRC          | 关闭    |                                       |  |  |  |  |

表3-2 停止模式的系统行为

- 1 MCGC1 中的 IREFSTEN 被置位,否则待机。

- 2 RTCSC中的RTCPS[3:0]在进入停止模式前不等于0,否则关闭

- 3 MCGC2 中的 EREFSTEN 被置位,否则待机。在 STOP3 模式下,高频范围 (MCGC2 中的 RANGE 被置位)要求 LVD 必须被开启。

#### MC9S08JS16RM中文手册(第三章 操作模式)

4 CTL 中的 USBEN 和 USBCTL0 中的 USBPHYEN 被置位,否则关闭。

# 第四章 存储器

# 4.1 简介 MC9S08JS16系列存储器映像

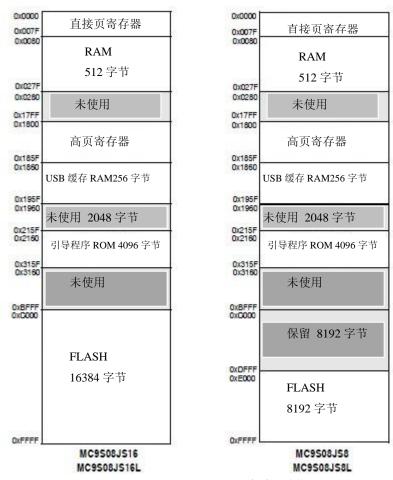

图 4-1 给出了 MC9S08JS16 系列 MCU 的存储器映像。MC9S08JS16 系列产品中的片内存储器包括 RAM,用于非易失性数据存储的 FLASH 程序存储器,I/O 和控制/状态寄存器。这些寄存器可分为以下三类:

直接页寄存器(0x0000-0x007F) 高页寄存器(0x1800-0x185F) 非易失性寄存器(0xFFB0-0xFFBF)

图4-1 MC9S08JS16系列存储器映像

# 4.1.1 复位和中断向量分配

表 4-1 为复位和中断向量地址的分配情况。该表中使用的向量名即为飞思卡尔提供的 MC9S08JS16 系列通用文件中使用的标签。关于复位,中断,中断优先级,和中断屏蔽控制 的更多细节,请参阅第 5 章,"复位,中断,和系统配置"。

表4-1 复位和中断向量

| 地址(高/低)       | 向量                    | 向量名 |

|---------------|-----------------------|-----|

| 0xFFC0:0xFFC1 | 未使用的向量空间 <sup>1</sup> | _   |

| 到           |           |           |

|-------------|-----------|-----------|

| 0xFFC2:FFC3 |           |           |

| 0xFFC4:FFC5 | RTC       | Vrtc      |

| 0xFFC6:FFC7 | 未使用的向量空间  | _         |

| 0xFFC8:FFC9 | 未使用的向量空间  | _         |

| 0xFFCA:FFCB | MTIM      | Vmtim     |

| 0xFFCC:FFCD | KBI       | Vkeyboard |

| 0xFFCE:FFCF |           |           |

| 到           | 未使用的向量空间  | _         |

| 0xFFD2:FFD3 |           |           |

| 0xFFD4:FFD5 | SCI 发送    | Vscitx    |

| 0xFFD6:FFD7 | SCI 接收    | Vscirx    |

| 0xFFD8:FFD9 | SCI 错误    | Vscierr   |

| 0xFFDA:FFDB |           |           |

| 到           | 保留        | _         |

| 0xFFE6:FFE7 |           |           |

| 0xFFE8:FFE9 | TPM 溢出    | Vtpmovf   |

| 0xFFEA:FFEB | TPM 通道 1  | Vtpmch1   |

| 0xFFEC:FFED | TPM 通道 0  | Vtpmch0   |

| 0xFFEE:FFEF | 未使用的向量空间  | _         |

| 0xFFF0:FFF1 | USB 状态    | Vusb      |

| 0xFFE6:FFE7 | TPM1 通道 4 | Vtpm1ch4  |

| 0xFFE8:FFE9 | TPM1 通道 3 | Vtpm1ch3  |

| 0xFFEA:FFEB | TPM1 通道 2 | Vtpm1ch2  |

| 0xFFEC:FFED | TPM1 通道 1 | Vtpm1ch1  |

| 0xFFEE:FFEF | TPM1 通道 0 | Vtpm1ch0  |

| 0xFFF0:FFF1 | 预留        | -         |

| 0xFFF2:FFF3 | USB状态     | Vusb      |

| 0xFFF4:FFF5 | SPI       | Vspi      |

| 0xFFF6:FFF7 | MCG锁损失    | Vlol      |

| 0xFFF8:FFF9 | 低电压检测     | Vlvd      |

| 0xFFFA:FFFB | IRQ       | Virq      |

| 0xFFFC:FFFD | SWI       | Vswi      |

| 0xFFFE:FFFF | 复位        | Vreset    |

<sup>1</sup> 未使用的向量空间可以作为通用 FLASH 存储空间来使用。然而,S08 系列 MCU 其他的芯片也许使用了这些地址作为中断向量。因此,如果要将代码移植到其他 MCU 必须小心使用这些地址空间。

# 4.2 寄存器地址和位分配

MC9S08JS16系列产品中的寄存器可分为以下三组:

直接页寄存器,位于存储器映像的前 128 个位置上,这些寄存器可以通过高效的直接寻址方式指令访问。

高页寄存器不经常使用,因此位于存储器映像中 0x1800 以上。在直接页中为频繁使用

的寄存器和变量留出了更多的空间。

非易失性寄存器,由 FLASH 存储器中 0xFFB0-0xFFBF 之间 16 个地址段组成。非易失性寄存器地址包括:

在复位时,加载到工作寄存器的三个值

一个8字节的后门对比密钥,可选择性的允许用户拥有对安全内存的受控制的访问权限。由于非易失性寄存器位于FLASH存储器中,它们必须像其它FLASH存储器地址一样进行擦除和编程。

直接页寄存器可以通过高效的直接寻址方式指令访问。位操纵指令可用于访问任何直接页寄存器中的任何位。表 4-2 总结了所有用户可访问的直接页寄存器和控制位。

表 4-2 所列的直接页寄存器可以使用更高效的直接寻址方式,只需要地址的低位字节。 正因为如此,第 1 栏中地址的较低字节用粗体显示。在表 4-3 和表 4-4 中,第 1 栏中的整个 地址都用粗体显示。在表 4-2,表 4-3,和表 4-4 中,第 2 栏中的寄存器名称用粗体显示以便与 右侧的位名称区分。与所列出的位不相关的单元格用阴影显示。带有 0 的阴影单元表示这个 未使用的位始终应为 0。带有破折号的阴影单元表示未使用的或预留的位,可以是 1 或 0。

表4-2 直接页寄存器汇总

| 地址: 0x0000 0x0001 0x0002 0x0003 0x0004- | 寄存器名称 PTAD PTADD PTBD PTBDD | 位 7 PTAD7 PTADD7 0 | 位 6<br>PTAD6<br>PTADD6 | 位 5<br>PTAD5<br>PTADD5 | 位 4<br>PTAD4<br>PTADD4 | 位3<br>PTAD3 | 位 2<br>PTAD2 | 位 1<br>PTAD1 | 位 0<br>PTAD0 |

|-----------------------------------------|-----------------------------|--------------------|------------------------|------------------------|------------------------|-------------|--------------|--------------|--------------|

| 0x0001<br>0x0002<br>0x0003              | PTADD PTBD PTBDD            | PTADD7             | PTADD6                 |                        |                        |             | PTAD2        | PTAD1        | PTAD0        |

| 0x0002<br>0x0003                        | PTBD<br>PTBDD               | 0                  |                        | PTADD5                 | PTADD4                 |             |              |              |              |

| 0x0003                                  | PTBDD                       |                    | 0                      |                        |                        | PTADD3      | PTADD2       | PTADD1       | PTADD0       |

| -                                       |                             | 0                  |                        | PTBD5                  | PTBD4                  | PTBD3       | PTBD2        | PTBD1        | PTBD0        |

| 0x0004-                                 |                             | Ü                  | 0                      | PTBDD5                 | PTBDD4                 | PTBDD3      | PTBDD2       | PTBDD1       | PTBDD0       |

|                                         | 文芸 成刀                       | _                  | _                      | _                      | _                      | _           | _            | _            | _            |

| 0x0007                                  | 预留                          | _                  | _                      | _                      | _                      | _           | _            | _            | _            |

| 0x0008                                  | MTIMSC                      | TOF                | TOIE                   | TRST                   | TSTP                   | 0           | 0            | 0            | 0            |

| 0x0009                                  | MTIMCLK                     | 0                  | 0                      | CLI                    | KS                     |             | P            | S            | <del>.</del> |

| 0x000A                                  | MTIMCNT                     |                    |                        |                        | COUN                   | T           |              |              |              |

| 0x000B                                  | MTIMMOD                     |                    |                        |                        | MOD                    | )           |              |              |              |

| 0x000C                                  | CRCH                        | 位 15               | 14                     | 13                     | 12                     | 11          | 10           | 9            | 位 8          |

| 0x000D                                  | CRCL                        | 位 7                | 6                      | 5                      | 4                      | 3           | 2            | 1            | 位 0          |

| 0x000E                                  | 预留                          | _                  | _                      | _                      | _                      | _           | _            | _            | _            |

| 0x000F                                  | 预留                          | _                  | _                      | _                      | _                      | _           | _            | _            | _            |

| 0x0010                                  | TPMSC                       | TOF                | TOIE                   | CPWMS                  | CLKSB                  | CLKSA       | PS2          | PS1          | PS0          |

| 0x0011                                  | TPMCNTH                     | 位 15               | 14                     | 13                     | 12                     | 11          | 10           | 9            | 位 8          |

| 0x0012                                  | TPMCNTL                     | 位 7                | 6                      | 5                      | 4                      | 3           | 2            | 1            | 位 0          |

| 0x0013                                  | TPMMODH                     | 位 15               | 14                     | 13                     | 12                     | 11          | 10           | 9            | 位 8          |

| 0x0014                                  | TPMMODL                     | 位 7                | 6                      | 5                      | 4                      | 3           | 2            | 1            | 位 0          |

| 0x0015                                  | TPMC0SC                     | CH0F               | CH0IE                  | MS0B                   | MS0A                   | ELS0B       | ELS0A        | 0            | 0            |

| 0x0016                                  | TPMC0VH                     | 位 15               | 14                     | 13                     | 12                     | 11          | 10           | 9            | 位 8          |

| 0x0017                                  | TPMC0VL                     | 位 7                | 6                      | 5                      | 4                      | 3           | 2            | 1            | 位 0          |

| 0x0018                                  | TPMC1SC                     | CH1F               | CH1IE                  | MS1B                   | MS1A                   | ELS1B       | ELS1A        | 0            | 0            |

| 0x0019                                  | TPMC1VH                     | 位 15               | 14                     | 13                     | 12                     | 11          | 10           | 9            | 位 8          |

| 0x001A                                  | TPMC1VL                     | 位 7                | 6                      | 5                      | 4                      | 3           | 2            | 1            | 位 0          |

| 0x001B                                  | IRQSC                       | 0                  | IRQPDD                 | IRQEDG                 | IRQPE                  | IRQF        | IRQACK       | IRQIE        | IRQMOD       |

| 0x001C                                  | KBISC                       | 0                  | 0                      | 0                      | 0                      | KBF         | KBACK        | KBIE         | KBMOD        |

| 0x001D            | KBIPE   | KBIPE7       | KBIPE6  | KBIPE5        | KBIPE4    | KBIPE3      | KBIPE2      | KBIPE1      | KBIPE0       |

|-------------------|---------|--------------|---------|---------------|-----------|-------------|-------------|-------------|--------------|

| 0x001E            | KBIES   | KBEDG7       | KBEDG6  | KBEDG5        | KBEDG4    | KBEDG3      | KBEDG2      | KBEDG<br>1  | KBEDG0       |

| 0x001F            | 预留      | _            | _       | _             | _         | _           | _           | _           | _            |

| 0x0020            | SCIBDH  | LBKDIE       | RXEDGIE | 0             | SBR12     | SBR11       | SBR10       | SBR9        | SBR8         |

| 0x0021            | SCIBDL  | SBR7         | SBR6    | SBR5          | SBR4      | SBR3        | SBR2        | SBR1        | SBR0         |

| 0x0022            | SCIC1   | LOOPS        | SCISWAI | RSRC          | M         | WAKE        | ILT         | PE          | PT           |

| 0x0023            | SCIC2   | TIE          | TCIE    | RIE           | ILIE      | TE          | RE          | RWU         | SBK          |

| 0x0024            | SCIS1   | TDRE         | TC      | RDRF          | IDLE      | OR          | NF          | FE          | RF           |

| 0x0025            | SCIS2   | LBKDIF       | RXEDGIF | 0             | RXINV     | RWUID       | BRK13       | LBKDE       | RAF          |

| 0x0026            | SCIC3   | R8           | Т8      | TXDIR         | TXINV     | ORIE        | NEIE        | FEIE        | PEIE         |

| 0x0027            | SCID    | 位 7          | 6       | 5             | 4         | 3           | 2           | 1           | 位 0          |

| 0x0028-<br>0x002F | 预留      | _            | _       | _             | _         | _           | _           | _           | _            |

| 0x0030            | SPIC1   | SPIE         | SPE     | SPTIE         | MSTR      | CPOL        | СРНА        | SSOE        | LSBFE        |

| 0x0031            | SPIC2   | SPMIE        | SPIMODE | 0             | MODFEN    | BIDIRO<br>E | 0           | SPISWA<br>I | SPC0         |

| 0x0032            | SPIBR   | 0            | SPPR2   | SPPR1         | SPPR0     | 0           | SPR2        | SPR1        | SPR0         |

| 0x0033            | SPIS    | SPRF         | SPMF    | SPTEF         | MODF      | 0           | 0           | 0           | 0            |

| 0x0034            | SPIDH   | 位 15         | 14      | 13            | 12        | 11          | 10          | 9           | 位 8          |

| 0x0035            | SPIDL   | 位 7          | 6       | 5             | 4         | 3           | 2           | 1           | 位 0          |

| 0x0036            | SPIMH   | 位 15         | 14      | 13            | 12        | 11          | 10          | 9           | 位 8          |

| 0x0037            | SPIML   | 位 7          | 6       | 5             | 4         | 3           | 2           | 1           | 位 0          |

| 0x0038-<br>0x003F | 预留      | _            | _       | _             | _         | _           | _           | _           | _            |

| 0x0040            | MCGC1   | CL           | .KS     |               | RDIV      |             | IREFS       | IRCLKE<br>N | IREFSTE<br>N |

| 0x0041            | MCGC2   | ВІ           | DIV     | RANGE         | HGO       | LP          | EREFS       | ERCLKE<br>N | EREFSTE<br>N |

| 0x0042            | MCGTRM  |              |         |               | TRIN      | Л           |             |             |              |

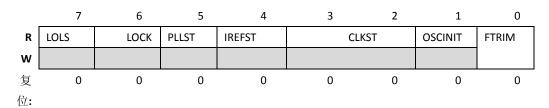

| 0x0043            | MCGSC   | LOLS         | LOCK    | PLLST         | IREFST    | CL          | KST         | OSCINI<br>T | FTRIM        |

| 0x0044            | MCGC3   | LOLIE        | PLLS    | CME           | ME 0 VDIV |             | DIV         |             |              |

| 0x0045-<br>0x0047 | 预留      | _            | _       | _             | _         | _           | _           | _           | _            |

| 0x0048            | RTCSC   | RTIF         | RTC     | LKS           | RTIE      |             | RT          | CPS         |              |

| 0x0049            | RTCCNT  |              | 1       |               | RTCC      | NT          |             |             |              |

| 0x004A            | RTCMOD  |              |         |               | RTCO      | MD          |             |             |              |

| 0x004B-           | 77 Co   |              |         |               |           |             |             |             |              |

| 0x004F            | 预留      | _            | _       | _             | _         |             |             | _           | _            |

| 0x0050            | USBCTL0 | USBRESE<br>T | USBPU   | USBRESM<br>EN | LPRESF    | 0           | USBVRE<br>N | 0           | USBPHY<br>EN |

| 0x0051-           | 预留      |              | _       | _             |           | _           |             | _           | _            |

|                   | ē       |              |         |               |           |             |             |             |              |

| 0x0057            |         |         |       |              |              |             |             |             |         |

|-------------------|---------|---------|-------|--------------|--------------|-------------|-------------|-------------|---------|

| 0x0058            | PERID   | 0       | 0     | ID5          | ID4          | ID3         | ID2         | ID1         | ID0     |

| 0x0059            | IDCOMP  | 1       | 1     | NID5         | NID4         | NID3        | NID2        | NID1        | NID0    |

| 0x005A            | REV     | REV7    | REV6  | REV5         | REV4         | REV3        | REV2        | REV1        | REV0    |

| 0x005B-<br>0x005E | 预留      | _       | _     | _            | _            | _           | П           | _           | _       |

| 0x005C            | IICD    |         |       |              | DATA         | A           |             |             |         |

| 0x005F            | 预留      | _       | _     | I            | _            | _           | I           | _           | _       |

| 0x0060            | INTSTAT | STALLF  | 0     | RESUMEF      | SLEEPF       | TOKDN<br>EF | SOFTOK<br>F | ERRORF      | USBRSTF |

| 0x0061            | INTENB  | STALL   | 0     | RESUME       | SLEEP        | TOKDN<br>E  | SOFTOK      | ERROR       | USBRST  |

| 0x0062            | ERRSTAT | BTSERRF | _     | BUFERRF      | BTOERRF      | DFN8F       | CRC16F      | CRC5F       | PIDERRF |

| 0x0063            | ERRENB  | BTSERR  | 0     | BUFERR       | BTOERR       | DFN8        | CRC16       | CRC5        | PIDERR  |

| 0x0064            | STAT    |         | ENDP  |              |              |             | ODD         | 0           | 0       |

| 0x0065            | CTL     | _       | _     | TSUSPEN<br>D | _            | _           | CRESUM<br>E | ODDRS<br>T  | USBEN   |

| 0x0066            | ADDR    | 0       | ADDR6 | ADDR5        | ADDR4        | ADDR3       | ADDR2       | ADDR1       | ADDR0   |

| 0x0067            | FRMNUML | 位 15    | 14    | 13           | 12           | 11          | 10          | 9           | 位 8     |

| 0x0068            | FRMNUMH | 位 7     | 6     | 5            | 4            | 3           | 2           | 1           | 位 0     |

| 0x0069-<br>0x006C | 预留      | _       | _     | I            | _            | _           | I           | _           | _       |

| 0x006D            | EPCTL0  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x006E            | EPCTL1  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x006F            | EPCTL2  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x0070            | EPCTL3  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x0071            | EPCTL4  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x0072            | EPCTL5  | 0       | 0     | 0            | EPCTLDI<br>S | EPRXEN      | EPTXEN      | EPSTAL<br>L | EPHSHK  |

| 0x0073            | EPCTL6  | SPRF    | SPMF  | SPTEF        | MODF         | 0           | 0           | 0           | 0       |

| 0x0074-<br>0x007F | 预留      |         | _     | _            | _            | _           | I           | _           | _       |

表 4-3 中列出的高页寄存器的访问频率比其它 I/O 和控制寄存器低很多,因此存放在可直接寻址的内存空间外,从 0x1800 开始。

注:

MCG 工厂调整值将会在任何复位发生之后自动装载进 0x180C 和 0x180D 寄存器中。

#### MC9S08JS16RM中文手册 (第四章 存储器)

表4-3 高页寄存器汇总

|         | 表4-3 高页寄存器汇总 |         |                  |        |           |        |        |        |        |

|---------|--------------|---------|------------------|--------|-----------|--------|--------|--------|--------|

| 地址      | 寄存器名称        | 位 7     | 6                | 5      | 4         | 3      | 2      | 1      | 位 0    |

| 0x1800  | SRS          | POR     | PIN              | COP    | ILOP      | ILAD   | LOC    | LVD    | 1      |

| 0x1801  | SBDFR        | 0       | 0                | 0      | 0         | 0      | 0      | 0      | BDFR   |

| 0x1802  | SOPT1        | CC      | )PT              | STOPE  | 1         | 0      | SPIFE  | 0      | 0      |

| 0x1803  | SOPT2        | COPCLKS | COPW             | 0      | 0         | 0      | SPIFE  | 0      | 0      |

| 0x1804  | 预留           | _       | _                | _      | _         | _      | _      | _      | -      |

| 0x1805  | 预留           | _       | _                | _      | _         | _      | _      | _      | _      |

| 0x1806  | SDIDH        | _       | _                | _      | _         | ID11   | ID10   | ID9    | ID8    |

| 0x1807  | SDIDL        | ID7     | ID6              | ID5    | ID4       | ID3    | ID2    | ID1    | ID0    |

| 0x1808  | 预留           | _       | _                | _      | _         | _      | _      | _      | 1      |

| 0x1809  | SPMSC1       | LVWF    | LVWACK           | LVWIE  | LVDRE     | LVDSE  | LVDE   | 0      | 0      |

| 0x180A  | SPMSC2       | 0       | 0                | LVDV   | LVWV      | PPDF   | PPDACK | 0      | PPDC   |

| 0x180B  | 预留           | _       | _                | _      | _         | _      | _      | _      | _      |

| 0x180C  | 为 FTRIM 存    |         | _                | _      | _         | _      | _      |        | _      |

| 0.11000 | 储预留          |         |                  |        |           |        |        |        |        |

|         | 为            |         |                  |        |           |        |        |        |        |

| 0x180D  | MCGTRIM      |         |                  |        | TRIM      | I      |        |        |        |

|         | 存储预留         |         |                  |        |           |        |        |        |        |

| 0x180E  | FPROTD       | _       | _                | _      | _         | _      | _      | _      | _      |

| 0x180F  | SIGNATUR     |         |                  |        | SIGNATURE | 信号量    |        |        |        |

|         | Е            |         | DIGINITIONE 旧 7里 |        |           |        |        |        |        |

| 0x1810  | DBGCAH       | 位 15    | 14               | 13     | 12        | 11     | 10     | 9      | 位 8    |

| 0x1811  | DBGCAL       | 位 7     | 6                | 5      | 4         | 3      | 2      | 1      | 位 0    |

| 0x1812  | DBGCBH       | 位 15    | 14               | 13     | 12        | 11     | 10     | 9      | 位 8    |

| 0x1813  | DBGCBL       | 位 7     | 6                | 5      | 4         | 3      | 2      | 1      | 位 0    |

| 0x1814  | DBGFH        | 位 15    | 14               | 13     | 12        | 11     | 10     | 9      | 位 8    |

| 0x1815  | DBGFL        | 位 7     | 6                | 5      | 4         | 3      | 2      | 1      | 位 0    |

| 0x1816  | DBGC         | DBGEN   | ARM              | TAG    | BRKEN     | RWA    | RWAEN  | RWB    | RWBEN  |

| 0x1817  | DBGT         | TRGSEL  | BEGIN            | 0      | 0         | TRG3   | TRG2   | TRG1   | TRG0   |

| 0x1818  | DBGS         | AF      | BF               | ARMF   | 0         | CNT3   | CNT2   | CNT1   | CNT0   |

| 0x1819- | 预留           | _       | _                | _      | _         | _      | _      | _      | _      |

| 0x181F  | 37.11        |         |                  |        |           |        |        |        |        |

| 0x1820  | FCDIV        | DIVLD   | PRDIV8           | DIV5   | DIV4      | DIV3   | DIV2   | DIV1   | DIV0   |

| 0x1821  | FOPT         | KEYEN   | FNORED           | 0      | 0         | 0      | 0      | SEC01  | SEC00  |

| 0x1822  | 预留           | _       | _                | _      | _         | _      | _      | _      |        |

| 0x1823  | FCNFG        | 0       | 0                | KEYACC | 0         | 0      | 0      | 0      | 0      |

| 0x1824  | FPROT        | FPS7    | FPS6             | FPS5   | FPS4      | FPS3   | FPS2   | FPS1   | FPDIS  |

| 0x1825  | FSTAT        | FCBEF   | FCCF             | FPVIOL | FACCERR   | 0      | FBLANK | 0      | 0      |

| 0x1826  | FCMD         | FCMD7   | FCMD6            | FCMD5  | FCMD4     | FCMD3  | FCMD2  | FCMD1  | FCMD0  |

| 0x1827- | 预留           |         |                  |        |           |        |        |        |        |

| 0x183F  | 1火田          |         |                  |        |           |        |        |        |        |

| 0x1840  | PTAPE        | PTAPE7  | PTAPE6           | PTAPE5 | PTAPE4    | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

|         |              |         |                  |        |           |        |        |        |        |

| 0x1841  | PTASE | PTASE7 | PTASE6 | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x1842  | PTADS | PTADS7 | PTADS6 | PTADS5 | PTADS4 | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| 0x1843  | 预留    | _      | _      | _      | -      | _      | -      | _      | _      |

| 0x1844  | PTBPE | 0      | 0      | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1845  | PTBSE | 0      | 0      | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x1846  | PTBDS | 0      | 0      | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x1847- | 预留    | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x185F  | J火田   | _      | _      | _      |        | _      |        | _      | _      |

表4-4 非易失性寄存器汇总

| -       |                    |                |                | 1    |        | 1    | 1    |       | 1     |

|---------|--------------------|----------------|----------------|------|--------|------|------|-------|-------|

| 地址      | 寄存器名称              | 位 7            | 6              | 5    | 4      | 3    | 2    | 1     | 位 0   |

| 0xxFFAE | 为 FTRIM 存储保留       | 0              | 0              | 0    | 0      | 0    | 0    | 0     | FTRIM |

| 0xxFFAF | 为 MCGTRIM 存储<br>保留 | TRIM           |                |      |        |      |      |       |       |

| 0xFFB0- | NUD A CHUEN        |                |                |      | o 슬+IL | ÷    |      |       |       |

| 0xFFB7  | NVBACKKEY          |                |                |      | 8 字节比较 | 文密钥  |      |       |       |

| 0xFFB8- |                    |                | FLASH 块高字节和校验值 |      |        |      |      |       |       |

| 0xFFBC  |                    | FLASH 块低字节和校验值 |                |      |        |      |      |       |       |

| 0xFFBA  |                    | 旁路和校验值         |                |      |        |      |      |       |       |

| 0xFFBB  | 为用户数据存储预<br>留      |                | 用户数据           |      |        |      |      |       |       |

| 0xFFBC  | 为用户数据存储预<br>留      | 用户数据           |                |      |        |      |      |       |       |

| 0xFFBD  | NVPROT             | FPS7           | FPS6           | FPS5 | FPS4   | FPS3 | FPS2 | FPS1  | FPS0  |

| 0xFFBE  |                    | FLASH 部分擦除信号量  |                |      |        |      |      |       |       |

| 0xFFBF  | NVOPT              | KEYEN          | FNORED         | 0    | 0      | 0    | 0    | SEC01 | SEC00 |

表 4-4 列出的非易失性 FLASH 寄存器,位于 FLASH 中。这些寄存器包括 1 个 8 字节的后门密钥,可选择性用于访问安全的内存资源。在复位过程中,FLASH 中非易失性寄存器区域的 NVPROT 和 NVOPT 内容被转移到高页寄存器中相应的 FPROT 和 FOPT 工作寄存器中,以控制安全和块保护选项。

MCG 出厂跳变值被存储在 FLASH 信息行 (IFR<sup>1</sup>),在任何复位发生之后被装载进入 MCGTRM 和 MCGSC 寄存器。在 FLASH,TRIM,和 FTRIM 中的内部参考跳变值可以被 第三方程序重新编程改变,且必须被用户程序拷贝到相应 MCG 寄存器来覆盖出厂值。

注:

当 MCU 处于激活 BDM 模式中,IFR 中的跳变值不会被装载,MCGTRM 寄存器复位值为 0x80,MCGSC 中的 FTRIM 位会复位为 0。

1 IFR — 非易失性信息存储空间,仅能在产品测试中被访问。在产品测试期间,系统初始化,设置和测试信息被存储在 IFR。这个信息不能在普通用户模式或背景调试模式中被读取或修改。

如果密钥启用(KEYEN)位为 1,那么 8 字节对比密钥可用于暂时脱离内存安全的限制。这种密钥机制只能通过在安全内存中运行的用户代码来访问。(安全密钥不能通过背景调试命令直接输入。)这个安全密钥可通过将 KEYEN 位设为 0 来完全禁用。如果这个安全密钥被禁用,那么如果需要,脱离安全限制的唯一方式是整体擦除 Flash(通常通过背景调试接口)并确认 Flash 已为空。为了避免在下一次复位后返回到安全模式,应该将安全位(SEC01: SEC00)设置为非安全状态 (1:0)。

0xFFBB 和 0xFFBC 被用来存储用户数据,例如用户的 MCG 跳变值。

#### 4.3 RAM (系统RAM)

MC9S08JS16 系列包括静态 RAM。RAM 中 0x0100 以下的地址可以使用更高效的直接寻址模式访问,而这一区域中的任何单一比特可以通过位操作指令(BCLR、BSET、BRCLR和 BRSET)访问。首选的方式是在这一区域中查找 RAM 最频繁访问的程序变量。

在 MCU 处于低功耗的等待、Stop2 或 Stop3 模式时,RAM 会保留数据。加电启动时,RAM 中的内容不会被初始化。如果电源电压没有降低到支持RAM 保留的电压最低值以下,RAM 数据就不会受到任何复位的影响。

为了实现与 M68HC05MCU 的兼容性,HCS08 会将堆栈指针复位为 0x00FF。在 MC9S08JS16 系列中,将堆栈指针重新初始化到 RAM 顶部,以便经常被访问的 RAM 变量和位寻址的程序变量可以使用直接寄存器。复位初始化程序 (其中的 RamLast 等于飞思卡尔通用文件中 RAM 的最高地址)中包含以下两个指令序列。

LDHX #RamLast+1 ;point one past RAM

TXS :SP<- (H:X-1)

在启用了安全性的情况下, RAM 被认为是一种安全的内存资源, 不能通过 BDM 或从 非安全内存中执行代码来访问。若欲了解有关安全特性的更详尽描述, 请参见 4.7, "安全性"。

#### 4.4 USB RAM

#### 4.5 引导程序ROM

引导程序 ROM 中装有擦除和编写 FLASH 存储器的代码。引导程序 ROM 从一个类如一台 PC 机的 USB 主设备处提供了快速而可靠的 FLASH 擦除和编写的过程

飞思卡尔提供了一个 PC GUI (图形用户接口),可以通过 UCB 接口与 ROM 中的引导程序进行通讯 (PC 作为主 USB 设备)。

用 PC GUI 工作,用户可以:

整体除整个 FLASH 阵列

部分擦除 FLASH 阵列——除开始 1KB 外擦除所有 FLASH 块

对 FLASH 编程

复位 MCU

注:

如果引导程序功能被使用, MCU 提供电压必须高于 4V。内部 USB 3.3V 电压调节器在进入引导程序模式时将被使能。

注:

USB 引导程序需要一个外部振荡器,且频率必须为 2 MHz, 4 MHz, 6 MHz, 8 MHz, 12 MHz, 或 16 MHz。引导程序代码可以自动识别外部振荡器。如果没有使用引导程序,就没有这样的限制。

注:

对引导程序的 USB 描述符是固定的: VID 是 0x15A2, PID 是 0x0038.用户程序只能使用它自身的描述符。

#### 4.5.1 外部信号描述

引导程序 ROM 的BLMS引脚决定了 MCU 是否在上电复位期间直接进入引导程序模式。 这个引脚只在上电复位 (POR) 期间被检查。

表 4-5 显示了引导程序 ROM 的信号特征。

表4-5 信号特征

| 信号   | 功能       | I/O |  |  |

|------|----------|-----|--|--|

| BLMS | 引导程序模式选择 | 1   |  |  |

#### 4.5.2 操作模式

任何复位之后,MCU 跳至引导程序 ROM 地址,在那里几个限制因子被检查来决定是跳至引导程序代码还是用户代码。引导程序ROM可以在引导程序模式或用户模式下被访问。这一节描述了在这两种模式下的非法操作和保护机制。

以下四个将会在每次 MCU 复位以后被检查

- BLMS引脚

- SIGNATURE 信号量字节

- FLASH 块 CRC 校验和

- CRC 旁路字节

#### 4.5.2.1 引导程序模式

引导程序模式可以在以下四种条件中进入:

- 1.上电复位(POR)期间,当BLMS引脚为低电平且BKGD/MS没有被拉低,将无条件的进入引导程序模式。

- 2. 上电复位(POR)期间,当BLMS引脚和 BKGD/MS 引脚为高电平时,一个 CHECKSUMBYPASS FLASH 空间将被检查。如果它的值不等于 0x00 或 0xFF,则进入引导程序模式。

- 3. 上电复位(POR)期间,当BLMS引脚和 BKGD/MS 引脚为高电平时,一个CHECKSUMBYPASS FLASH 空间将被检查。如果它的值等于 0xFF,将计算 FLASH 阵列的CRC 值并与一个 16 位 FLASHCRC 字相比较。如果不匹配,则进入引导程序模式。

- 4. 复位过后(除了上电复位以外),系统将检查 SIGNATURE 信号量。如果等于 0xC3,则进入引导程序模式。

#### 4.5.2.2 用户模式

用户模式可以在以下三种条件下进入:

- 1. 上 电 复 位 ( POR ) 期 间 , 当 BLMS 引 脚 和 BKGD/MS 引 脚 为 高 电 平 , 且 CHECKSUMBYPASS 字节等于 0x00 时,进入用户模式。

- 2. 上电复位(POR)期间,当BLMS引脚和 BKGD/MS 引脚为高电平,且CHECKSUMBYPASS 字节等于 0xFF 时,将计算 FLASH 阵列的 CRC 值并与一个 16 位FLASHCRC 字相比较。如果结果匹配,进入用户模式。

- 3.当一个复位发生(除了上电复位以外),如果 SIGNATURE 信号量不等于 0xC3,则进入用户模式。

#### 4.5.2.3 激活背景模式和引导程序模式仲栽

上电复位(POR)期间,当BLMS引脚和BKGD/MS引脚为低电平,则进入激活背景模

式。

#### 4.5.2.4 禁止FLASH保护

通过向 FPROTD(FLASH 保护失败寄存器)地址连续写入 0x55 和 0xAA,然后将 FPROT 的 FPDIS 位置 1,来禁止 FLASH 区段的保护。

#### 4.5.3 FLASH存储映像

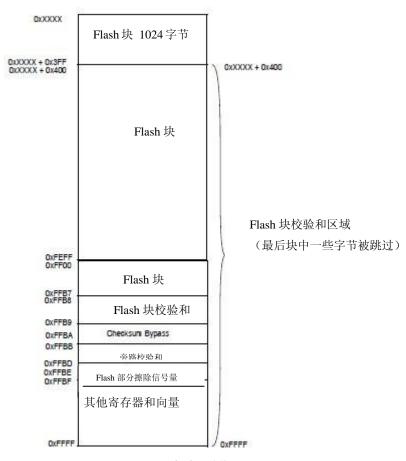

引导程序的通用 FLASH 存储映像显示于图 4-2。

- FLASH 块校验和存储于 0xFBB8(校验和高字节)和 0xFBB9(校验和低字节)

- 校验和旁路信息存储于 0xFFBA

- FLASH 部分擦除信号量存储于 0xFFBE

图4-2 通用FLASH存储器映像

旁路校验和的值靠用户编程设定。这个值只在上电复位之后被引导程序检查。这个字节的旁路校验和的值显示了 FLASH 块校验和是否会被计算,和在开始的 1KB 地址空间之后的 FLASH 区段是否被用作 EEPROM。当这个值不是 0x00 或 0xFF 时,不计算 FLASH 块的校验和,系统直接跳至引导程序入口。当值等于 0xFF 时,在上电复位之后 FLASH 块的校验和将会被计算。当值等于 0x00 时,不计算 FLASH 块的校验和,MCU 跳至用户程序入口处,在开始的 1KB 地址空间之后的 FLASH 区段将被用作 EEPROM。

芯片的出厂值为 0xFF。

注:

开始的 1KB FLASH 段不进行 CRC 校验计算,所以用户可以将这个区域用作 EEPROM。如果用户需

要用除此之外的其他 FLASH 空间,他们就需要重新计算 CRC,且重新编写 CRC 校验和来保证上电复位之后对地址空间的可靠访问。

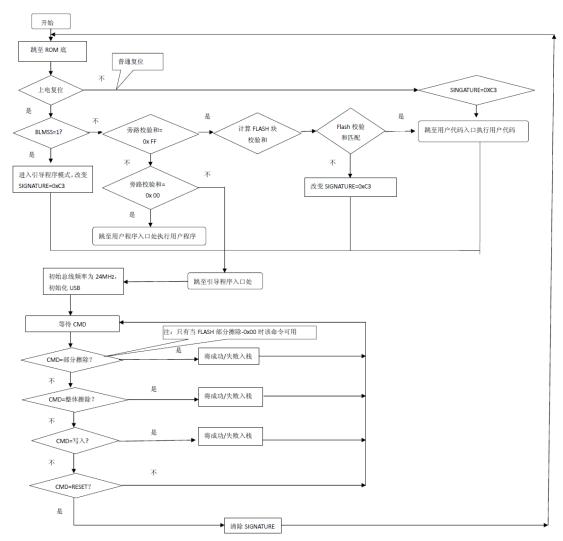

### 4.5.4 引导程序操作

这节描述了引导程序机制和引导程序流程图。

引导程序位于引导程序 ROM。用户可以对 FLASH 进行擦除和写入当:

- 讲入引导程序模式

- 计算出的 FLASH 块校验和和预置的 FLASH 块校验和在上电复位之后不匹配。

- 寄存器中的 SIGNATURE 信号量匹配。

#### 4.5.4.1 FLASH块校验和

上电复位(POR)时,如果 BLMSS=0 且旁路校验和的值为 0xFF 时,引导程序将计算 FLASH 的校验和。这个校验和从开始 1KB 之后的 FLASH 开始算起到 0xFFFF 为止(FLASH 最末页中部分字节被跳过)。开始的 1KB FLASH 不包含在校验和当中,所以用户可以将它当做伪 EEPROM 使用。这个计算出来的校验和将和事先写入 FLASH 中两个字节(FLASHCRC)的值相比较,如果校验和匹配,之前的引导程序操作就是成功的,MCU 跳至用户程序的入口处开始执行用户代码。如果校验和不匹配,它就会跳至引导程序入口处等待指令。

FLASH 块校验和的计算使用 16 位 CRC。

JS16FLASH 块校验和的范围是 0xC400-0xFFAD 和 0xFFC0-0xFFFF, JS8FLASH 块校验 范围是 0xE400-0xFFAD 和 0xFFC0-0xFFFF。

#### 4.5.4.2 SIGNATURE 信号量寄存器

在常规复位期间,引导程序检查 SIGNATURE 信号量寄存器。如果 SIGNATURE=0xC3,则 MCU 跳至引导程序入口处等待指令。如果不是,则它跳至用户程序入口处开始执行用户代码。

用户被要求在他们的程序代码中提供一个机制来将 SIGNATURE 的值设为 0xC3,以及 开始一次复位当他们希望在一次用户代码被成功写入之后重新进入引导程序模式。可选方案 是,进入 BKGD 模式,SIGNATURE 可以用 BDM 指令来更新,BKGD 引脚为高电平时可以 引发复位。

#### 4.5.4.3 FLASH部分擦除信号量

FLASH 部分擦除的值依靠用户写入。只有当这个值被写为 0x00 时,引导程序支持部分擦除 FLASH 阵列命令。

芯片的出厂值为 0xFF。

#### 4.5.4.4 流程图

图4-3引导程序流程图

#### 4.6 FLASH

FLASH 存储器主要用于保存程序。在线编程使正在运行的程序可以在应用产品的最终组装完成后上载到 Flash 中。我们可以通过单线背景调试接口对阵列进行编程。由于 FLASH 擦除和编程操作不需要特殊的电压,所以也可以通过其他软件控制的通信路径来实现应用编程。有关在线和应用内编程的更详尽描述,请参见"HCS08 系列参考手册,第 1 卷"(飞思卡尔半导体文件,编号 HCS08RMv1)。

# 4.6.1 特点

FLASH 存储器特点包括:

- FLASH 大小

- ——MC9S08JS16- 16384 字节(32 页,每页 512 字节) -

- ——MC9S08JS8-8192 字节(16页,每页 512 字节)

- 单电源写入和擦除

- 命令界面提供快速写入和擦除操作

- 在典型的电压和温度下有最多可达 100000 个写入/擦除周期

- 灵活的块保护

- FLASH 和 RAM 的安全特性

- 自动关闭电源以获得低频读取

### 4.6.2 写入和擦除时间

在接受任何写入或擦除命令前,必须通过写 FLASH 时钟分频寄存器 (FCDIV) 以将 Flash 模块的内部时钟设置为 150kHz ~200kHz 之间的频率( $f_{FCLK}$ )(请参见 4.8.1"FLASH 时钟分频寄存器(FCDIV)")。这个寄存器只能写入一次,因此这一写入操作通常是在复位 初始化过程中执行的。如果 FSTAT 寄存器的 FACCERR 访问错误标志位被置位,FCDIV 不能被写入。用户必须确保在写入 FCDIV 寄存器之前没有将 FACCERR 置为 1。命令处理器 使用时钟 ( $1/f_{FCLK}$ )的一个周期来对写入和擦除脉冲定时。命令处理器利用这些定时脉冲的一个整数值来完成编程或擦除命令。

表 4-6 给出了写入和擦除时间。总线时钟频率和 FCDIV 决定 FCLK 的频率( $f_{FCLK}$ )。 一个 FCLK 周期为  $t_{FCLK}=1/f_{FCLK}$ 。定时器显示为多个 FCLK 循环和一个绝对时间( $t_{FCLK}=5~\mu s$ )。显示的写入和擦除时间包括命令状态机的开销及写入和擦除电压的启用及禁用的时间。

| 参数   | FCLK循环 | FCLK = 200 kHz 时的时间 |

|------|--------|---------------------|

| 字节程序 | 9      | 45 μs               |

| 批量程序 | 4      | 20 μs¹              |

| 页擦除  | 4000   | 20 ms               |

| 整体擦除 | 20,000 | 100 ms              |

表4-5 编程和擦除时间

# 4.6.3 编程和擦除命令的执行

下面列出执行任何命令的步骤。在执行命令之前 FCDIV 寄存器必须被初始化,任何错误标志都需要被清除。命令执行的步骤是:

1、将一个数据值写入到 Flash 阵列中的一个地址中。该地址和写入的数据信息被锁定到 Flash 接口上。这一写入操作是任何命令序列中要求的第一步。对于擦除和空白检查命令,这些数据的值并不重要。对于页擦除命令,地址可以是将要擦除的 Flash512 字节页面中的任何地址。对于整体擦除和空检查命令,地址可以是 Flash 存储器中的任何地址。512 字节的整个页面是 FLASH 中能被擦除的最小块。

注意:

在擦除操作成功之后,不要对 FLASH 中的任意字节写入超过一次。如果没有先对 FLASH 存储器进行整体擦除或擦除字节所在的页面,对已经写入的字节重新写入是不被允许的。写入前没先擦除可能会扰乱储存在 FLASH 中的数据。

- 2、将命令代码写入到 FCMD 中。 6 个有效的命令分别是空白检查 (0x05)、字节写入(0x20)、突发模式写入(0x25)、页擦除(0x40)、整体擦除(0x41)和页擦除终止(0x47)。命令代码被锁定到命令缓冲器中。

- 3、将一个 1 写入到 FSTAT 中的 FCBEF 位上,以清除 FCBEF 并发起命令 (包括 其地址和数据信息)。

在写内存阵列之后到写 1 清零 FCBEF 发起完整命令之前的任何时候,可以通过向

<sup>1</sup> 包括启动/终止开销

FCBEF 中写入一个"0",来使部分命令序列失效。以这种方式终止一个命令会将 FACCERR 访问错误标记置 1,而这个标记必须在开始一个新命令之前清零。

整个过程必须遵守严格的监控流程,否则命令将不会被接受。通过这种方式可以最大限度地降低无意中修改 FLASH 存储器内容的可能性。命令完整标记 (FCCF)用于指示一条命令是否完成。通过清除 FCBEF 来开始执行命令,命令序列被完成。 图 4-4 是除突发模式写入和页擦除终止以外的所有命令的执行流程。在使用任何 FLASH 命令之前,FCDIV 寄存器必须初始化。复位后,这只能执行一次。

# 4.6.4 批量写入

突发模式写入命令用来写入连续的字节,相比较标准写入命令需要较少的时间。因为不需要屏蔽两次写入操作之间加在 Flash 阵列的高电压。通常情况下,当发起一个写入或擦除命令,必须启用与 Flash 相关的一个内部电荷泵用于为阵列提供高电压。命令执行完成后,该电荷泵会被关闭。如果满足下面两个条件,当突发模式写入操作完成,电荷泵仍然保持打

开:

- 在本次操作完成之前下次,下次突发模式写入命令已经排队等候。

- 下一个连续地址选择了和当前正在写入的字节具有相同的物理行的字节。FLASH 内存行包括 64 个字节。每行的字节通过地址的 A5 到 A0 选择。一个新行的起始地址中的 A5 到 A0 全零。

在突发模式中写入一系列连续字节中的第一个所花的时间与正常模式中写入一个字节的时间是相同的,假设满足上述两个条件,后续字节将以突发模式写入。在下一个连续的地址是另一行的情况下,字节的写入时间将会是标准时间而不是突发时间。这因为加在阵列上的高电压将被屏蔽然后重新开启。如果在第一次命令结束之前新的命令没有排在队列中,电荷泵将被屏蔽,阵列上的高电压将被移除。

# 4.6.5 访问错误

无论何时只要违反了命令执行协议,将产生访问错误.

任何下列动作将会导致 FSTAT 中的访问错误标志 (FACCERR) 置位。在任何命令执行之前,FACCERR 位必须通过对 FSTAT 中的 FACCERR 写 1 的方式清除。

● 在写 FCDIV 寄存器设置内部 FLASH 时钟频率之前,写 FLASH 地址

- 写 FLASH 地址的同时 FCBEF 没有被设置(直到命令缓存清空,才能开始一个新命令.)

- 在登记先前的命令之前,第二次写 FLASH 地址(每一个命令只对 FLASH 写一次.)

- 在登记先前的命令之前,第二次写 FCMD (每一次命令只对 FCMD 写一次.)

- 写 FLASH 地址之后设置除 FCMD 以外其他任何 FLASH 控制寄存器

- 写(0x05, 0x20, 0x25, 0x40, or 0x41) 之外的任何命令代码到 FCMD

- 在写命令到 FCMD 后访问(读或写)任何 FLASH 控制寄存器而不是在写入 FSTAT (为了清除 FCBEF 和登记命令)

- 当正在执行写入和擦除命令时 MCU 进入停止模式. (命令失败.)

- 当 MCU 处于安全状态时,用背景调试命令写字节写入、突发模式写入和页擦除这些命令(当 MCU 处于安全状态时,背景调试控制器只能进行空白检测和整体擦除命令)。

- 向 FCBEF 位写 0 取消一个未完成的命令。

### 4.6.6 FLASH块保护

块保护特点防止了 FLASH 的保护块被写入和擦除改变。块保护由 FLASH 保护寄存器 (FPROT) 控制。当使能,块保护从任何低于 FLASH 最后字节, 0xFFFF, 的任何 512 个字节边界开始。(参看 4.8.4, "FLASH 保护寄存器 (FPROT 和 NVPROT)")。

退出复位后,FPROT 用位于 FLASH 存储器中非易失寄存器块的 NVPROT 位置的内容加载。FPROT 不能用应用软件直接改变,所以一个失控的程序不能改变块保护的设置。因为 NVPROT 在 FLASH 最后 512 字节之中,如果任何数量的存储器被保护,NVPROT 自己也被保护,并且不能被应用软件(有意的或无意的)改变。背景调试命令能够写 FPROT,这是一种擦除和编程保护了的 FLASH 存储器的方法。

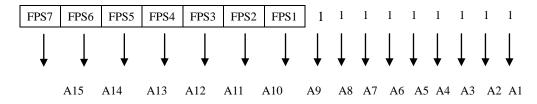

下图举例说明了块保护机制。FPS 位用作未保护存储区最后一个地址的高位。如图所示地址由 FPS7:FPS1 连接上逻辑 1 组成。例如,为了保护存储器中最后的 1536 个字节(地址从 0xFA00 到 0xFFFF), FPS 位需设置为 1111100,产生的值 0xF9FF 是存储器中最后未保护的地址。除了对 FPS 位写入正确的值,FPDIS(NVPROT 中的 0 位)必须被写入为逻辑 0 以确保块保护。因此值 0xF8 必须写入到 NVPROT 以确保地址 0xFA00 到 0xFFFF 被保护。

图4-6 块保护机制

块保护的一个用途是为引导程序提供一个保护了的 FLASH 存储区域。这样引导程序就可以用于擦除并且重新写剩余的 FLASH 存储器。因为引导程序被保护,所以即使 MCU 在写入或者擦除操作过程中掉电,该程序也是完整的。

# 4.6.7向量重定向

无论何时使能块保护,复位和中断矢量将会被保护。矢量重定向允许用户不用未保护引导程序和复位矢量空间就能修改中断矢量信息。矢量变向通过对位于0xFFBF地址的NVOPT中FNORED位写入为0使能。为产生重定向,通过对位于0xFFBD的NVPROT写入使至少

一些而不是全部 FLASH 存储区受到块保护。所有的中断矢量(位于存储器 0xFFC0-0xFFFD)都会重定向,而复位矢量(位于存储器 0xFFFE-0xFFFF)则不会重定向。

例如,如果 FLASH 的 512 字节受到保护,保护的区域地址是从 0xFE00 到 0xFFFF。中断矢量(0xFFC0-0xFFFD)重定向到位于 0xFDC0-0xFDFD。以 TPM1 溢出中断为例,0xFDE0:FDE1 中的值而不是 0xFFE0:FFE1 中的值将被中断向量使用。这就允许用户将新的程序代码和新的向量值写入 FALSH 中未被保护的部分,而包含默认向量地址的被保护区域不被改写。

### 4.7 安全性

MC9S08JS16使用硬件电路来防止对 FLASH 存储器和 RAM 存储器的数据的非法访问。 当使用安全机制时,FLASH 和 RAM 被认为是被保护资源资源。直接页寄存器,高页寄存器和背景调试控制器被认为是非被保护资源。在被保护存储器中执行的程序可正常访问任何 MCU 存储器和资源。试图用非被保护存储空间中执行的程序或通过背景调试接口对一个被保护存储器的访问将会被屏蔽(写被忽略,读返回 0)。

是否采取安全机制取决于非易失性寄存器 FOPT 中两个位(SEC01:SEC00)的状态。在复位过程中,非易失的 NVOPT 的内容从 FLASH 复制到在高页面寄存器空间的正在工作的 FOPT 寄存器。用户能在对 FLASH 存储器写入的同时通过写入 NVOPT 来采取安全机制。1:0 状态解除安全机制,其它三种组合则采取安全机制。注意擦除态(1:1)也让 MCU 被保护。在开发过程中,无论何时只要 FLASH 被擦除,立即对 NVOPT 中的 SEC00 位编程为 0,使 SEC01:SEC00 = 1:0。这让 MCU 在随后的复位后保持非被保护状态。

当 MCU 处于被保护态时,片内调试模块将不能被使能。这个独立的背景调试控制器仍然用于对未保护资源执行背景存储器访问命令。

用户可以通过 8 字节的后门密钥来允许或者禁止安全机制。如果 NVOPT 或者 FOPT 中的非易失性位 KEYEN 是 0,后门密钥是无效的,这时如果没有擦除整个的 FLASH 就没有方法离开安全模式。如果 KEYEN 是 1,一个在安全模式下的用户程序可以通过以下的方法暂时离开安全模式:

用户可以通过 8 字节的后门密钥来允许或者禁止安全机制。如果 NVOPT 或者 FOPT 中的非易失性位 KEYEN 是 0,后门密钥是无效的,这时如果没有擦除整个的 FLASH 就没有方法离开安全模式。如果 KEYEN 是 1,一个在安全模式下的用户程序可以通过以下的方法暂时离开安全模式:

- 1.对 FCNFG 寄存器中 KEYACC 写 1。这让 FLASH 模块对后门比较钥匙位置 (NVBACKKEY 到 NVBACKKEY+7) 的写操作解释为与钥匙相比较的值,而不是 FLASH 编程或者擦除命令的第一步。

- 2. 写用户进入钥匙的值到 NVBACKKEY 到 NVBACKKEY+7 的位置。这些写必须按照 开始于 NVBACKKEY,结束于 NVBACKKEY+7 上的值这样的顺序。这些写中将不会用到 STHX,因为这些写不能在相邻总线周期中完成。用户软件通常从 MCU 系统外面通过一种通讯接口,例如串口,获得钥匙代码。

- 3. 写 FCNFG 寄存器中的 KEYACC 为 0。如果刚写下的 8 字节钥匙与存储在 FLASH 中的钥匙相匹配, SEC01:SEC00 自动改变为 1:0, 在下次复位前都会禁用安全机制。

安全密钥只能从安全存储器 (RAM 或 FLASH) 写入。如果没有安全用户程序的协调不能由背景调试命令进入。

后门密钥(NVBACKKEY 到 NVBACKKEY+7)分布在FLASH存储器的非易失性寄存器空间中,因此用户可以象写其他FLASH寄存器一样写这些寄存器。这个非易失性的寄存

器与复位和中断向量一起都位于同样的一块 512 字节的 FLASH 存储区域中,所以块保护这块区域也就保护了后门密钥。块保护不能通过用户的应用程序改变,因此,如果向量空间是块保护空间,这个后门安全密钥机制永远不能改变块保护、安全设置和后门密钥。

安全模式可以通过背景调试接口按照下面的步骤来消除:

- 1. 通过写 FPROT 屏蔽任何块保护。在 MC9S08JS16 系列中,当 FPROTD 被置位,FPROT 可以被改变。

- 2. 如果必要,则整体擦除 FLASH。

- 3. 空检查 FLASH。如果 FLASH 被完全擦除,直到下次复位不采取安全机制。 为避免下次复位后返回安全模式,写入 NVOPT 使 SEC01:SEC00 = 1:0。

### 4.8 FLASH寄存器和控制位

FLASH 模块有 9 个 8 位的寄存器位于高地址页寄存器空间, 2 个位于 FLASH 存储器的非易失性寄存器空间, 当复位时, 内容被复制到相应的高页区域的控制寄存器。同样也有一个 8 字节的密钥在 FLASH 存储器中。表 4-3 和表 4-4 列出了所有 FLASH 寄存器的绝对地址。这里通过这些寄存器和控制位的名称来引用它们。通常, Freescale 提供一个通用文件或头文件把它们的名称翻译为绝对地址。

### 4.8.1 FLASH时钟分频寄存器(FCDIV)

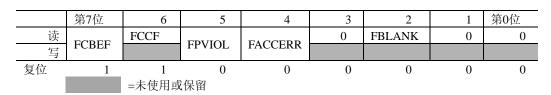

该寄存器的第7位是一个只读标记。6:0位可以在任何时候读取但只能写入一次。在 开始任何擦除或写入操作之前,写入该寄存器以将非易失性内存系统的时钟频率设置在可接 受的限度内。

|    | 第7位   | 6      | 5    | 4    | 3    | 2     | 1    | 第0位  |

|----|-------|--------|------|------|------|-------|------|------|

| 读  | DIVLD | DDDIVO | DIV5 | DIV4 | DIV3 | DIVIO | DIVI | DIVO |

| 写  |       | PRDIV8 | DIVS | DIV4 | DIVS | DIV2  | DIV1 | DIV0 |

| 复位 | 0     | 0      | 0    | 0    | 0    | 0     | 0    | 0    |

|    |       | =未使用或  | 保留   |      |      |       |      |      |

图4-7 FLASH时钟分频寄存器(FCDIV)

#### 表4-7 FCDIV寄存器字段描述

| 字段       | 描述                                                  |

|----------|-----------------------------------------------------|

|          | Divisor 加载状态标识 — 当置 1 时,这个只读状态标记指出 FCDIV 寄存器自从复位后已有 |

| 7        | 写入。复位会清除该位而且第一次写入该寄存器的操作将导致该位被置 1,不管写入什么数据。         |

| DIVLD    | 0 FCDIV 自复位后没有写入;Flash 和 EEPROM 的擦除和写入操作被禁止。        |

|          | 1 FCDIV 自复位后已写入; Flash 和 EEPROM 的擦除和写入操作已开启。        |

| 6        | Flash时钟8预分频 (分频)                                    |

| PRDIV8   | 0 Flash 钟分频器的时钟输入为总线速率时钟。                           |

| PRDIVO   | 1 Flash 时钟分频器的时钟输入为总线速率时钟除以8。                       |

|          | 时钟分频位——FLASH时钟分频器通过DIV5: DIV0这六位加上1的值来对总线时钟频率(或者    |

| 5:0      | 当PRDIV8=1时是总线时钟频率的八分之一)进行分频。在对FLASH进行操作时,内部时钟必      |

|          | 须降到150KHz~200KHz。擦除/写入操作的时序脉冲是内部FLASH工作时钟的一个时钟周期,   |

| DIV[5:0] | 所以擦/写的时间相应的在6.7μs~5μs。自动的写入逻辑使用这个时钟周期的整数倍时间完成擦除     |

|          | 或写入操作。参考等式4-1,等式4-2和表4-7。                           |

| ·        | if PRDIV8 = 0 fECLK = fBus $\div$ (DIV + 1) Eqn 4-1 |

if PRDIV8 = 0 — fFCLK = fBus  $\div$  (DIV + 1) if PRDIV8 = 1 — fFCLK = fBus  $\div$  (8 × (DIV + 1)) Eqn. 4-1 Eqn. 4-2

表 4-8 列出了对 PRDIV8 和 DIV5:DIV0 设置不同数值时的 FLASH 时钟频率。

表4-7 FLASH时钟分频器设置

|              |                     | · ·          |               |                                 |

|--------------|---------------------|--------------|---------------|---------------------------------|

| $ m f_{BUS}$ | PRDIV8<br>(二进<br>制) | DIV<br>(十进制) | $f_{ m FCLK}$ | 编程/擦除时序脉冲<br>(最小5 μs, 最大6.7 μs) |